================================================== 1. Registers Registers are tiny, very fast storage locations inside the CPU. RV32I has 32 integer registers: Each register is 32 bits wide. You…

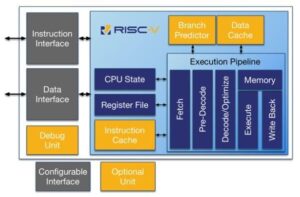

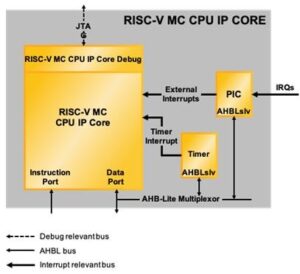

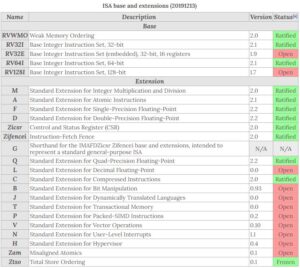

1. What is RISC-V? RISC-V is an Instruction Set Architecture (ISA). An ISA is the rulebook that defines: RISC-V is special because it is: RISC…

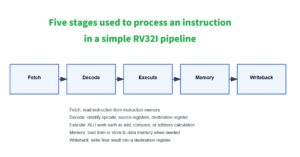

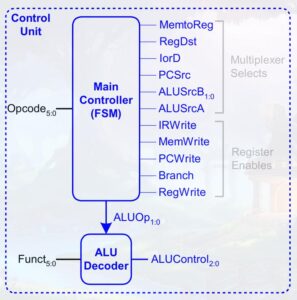

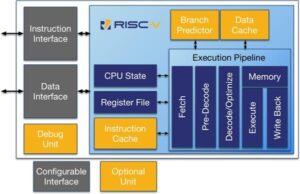

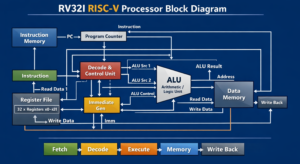

🧠 RV32I vs PicoRV32 — Visual Diagrams (Deep Mapping) 🟣 1. RV32I Single-Cycle (Your Diagram Style) 🔎 How to read it: Everything happens in parallel…

🚀 RV32I Tutorial #2: What is a Register File? Why Every CPU Needs It If RV32I defines what a CPU can do, then the…

🚀 RV32I Tutorial #1: What is RV32I? The Real Starting Point of a CPU Most people think CPUs understand code. They don’t. A CPU only…

Here’s a practical, no-fluff RV32I FPGA implementation roadmap — focused on getting you from zero → running code on hardware. hase 0 — Setup (1…

🔹 1. What is RV32I? RV32I is the base instruction set of the RISC-V architecture. RV = RISC-V 32 = 32-bit (registers are 32 bits…

The register-register instruction format can directly operate on the data in registers without involving memory read or write operations, making it faster. R-Type instructions are…

1. Instruction Set Encoding This article will continue the introduction of RISC-V and introduce the encoding structure of the RISC-V instruction set, as well as…

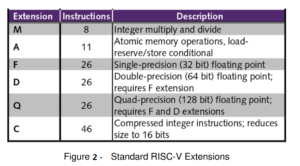

1.RISC-V Instruction Set Architecture Features The RISC-V instruction set has standard 32-bit architecture as well as 64-bit and 128-bit architectures. The general-purpose registers in the…