🔹 1. What is RV32I?

RV32I is the base instruction set of the RISC-V architecture.

- RV = RISC-V

- 32 = 32-bit (registers are 32 bits wide)

- I = Integer instruction set (the minimal core)

👉 Think of RV32I as the “minimum brain” a CPU needs to function.

If you build a CPU (especially on FPGA), RV32I is the starting point.

🔹 2. What Does RV32I Include?

RV32I defines a small, clean set of instructions:

🧩 Core Capabilities

- Arithmetic:

ADD,SUB - Logic:

AND,OR,XOR - Memory:

LW(load),SW(store) - Control flow:

BEQ,BNE,JAL - Immediate ops:

ADDI,ORI

👉 Around 40–50 instructions total

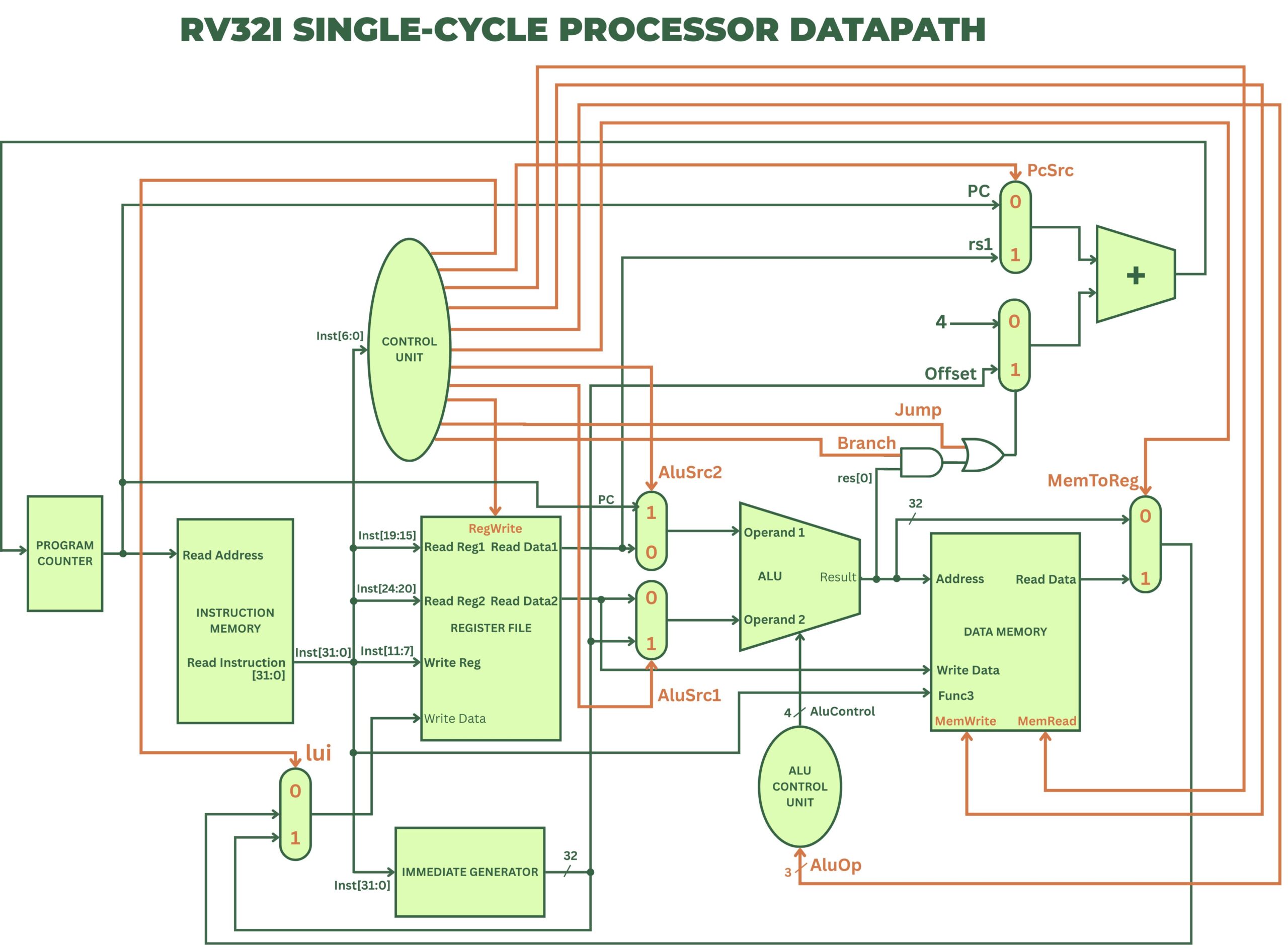

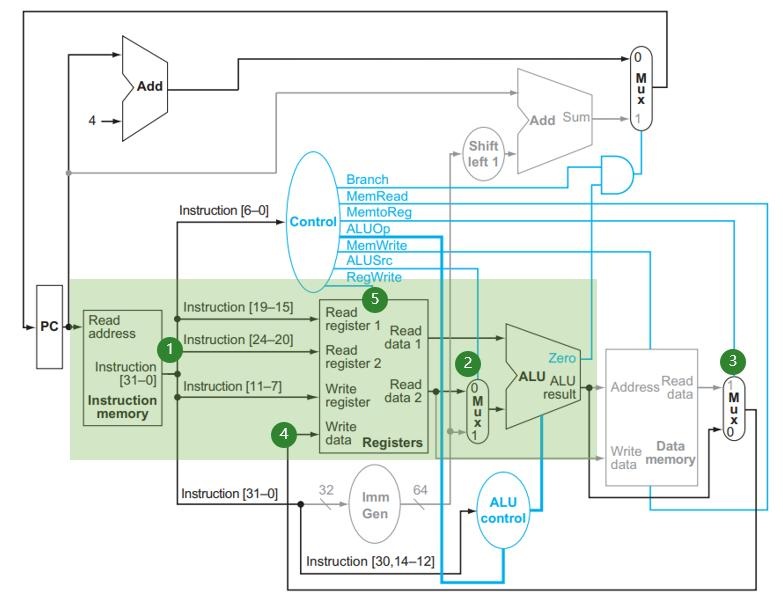

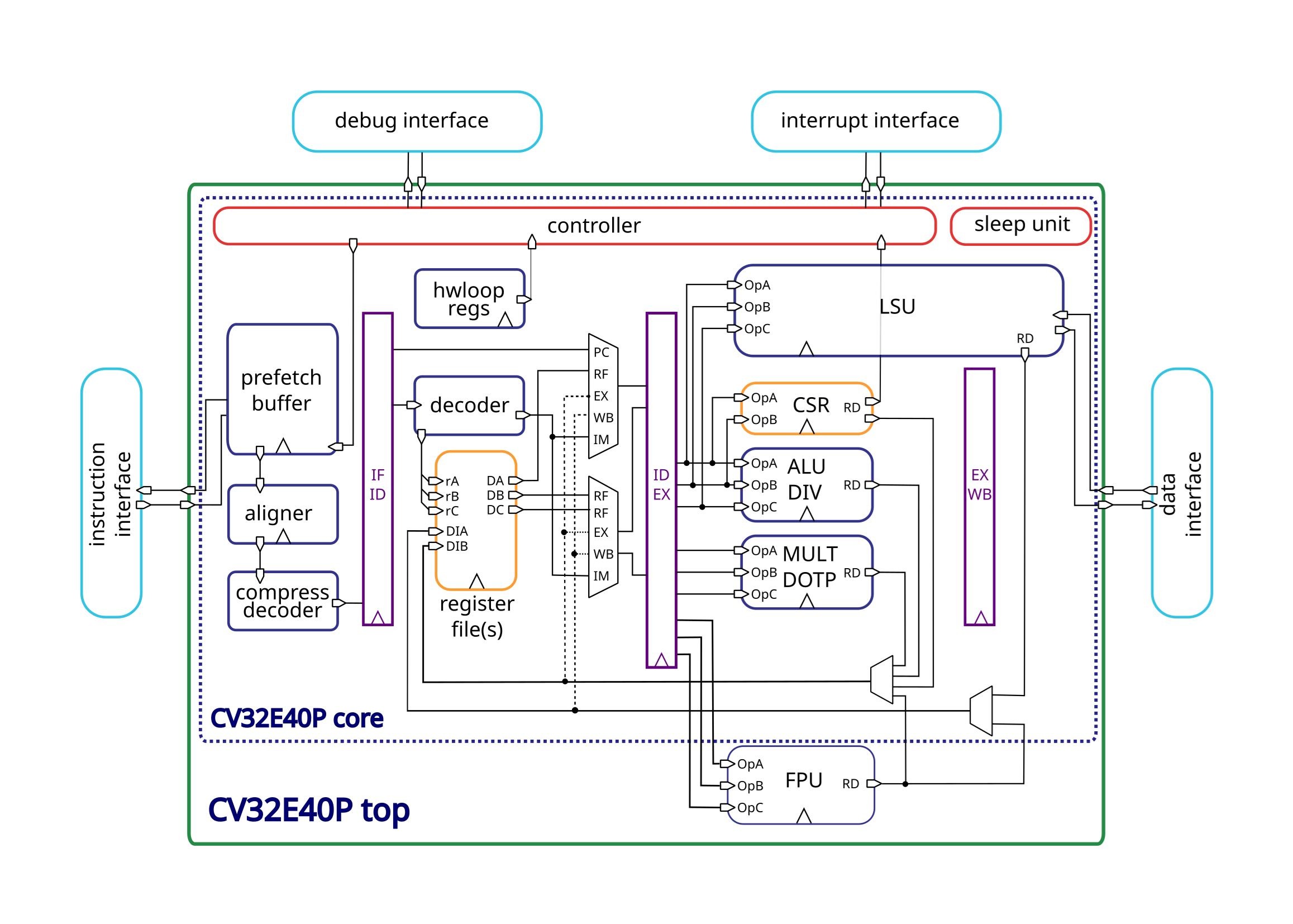

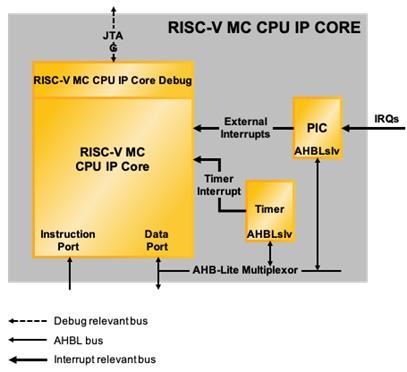

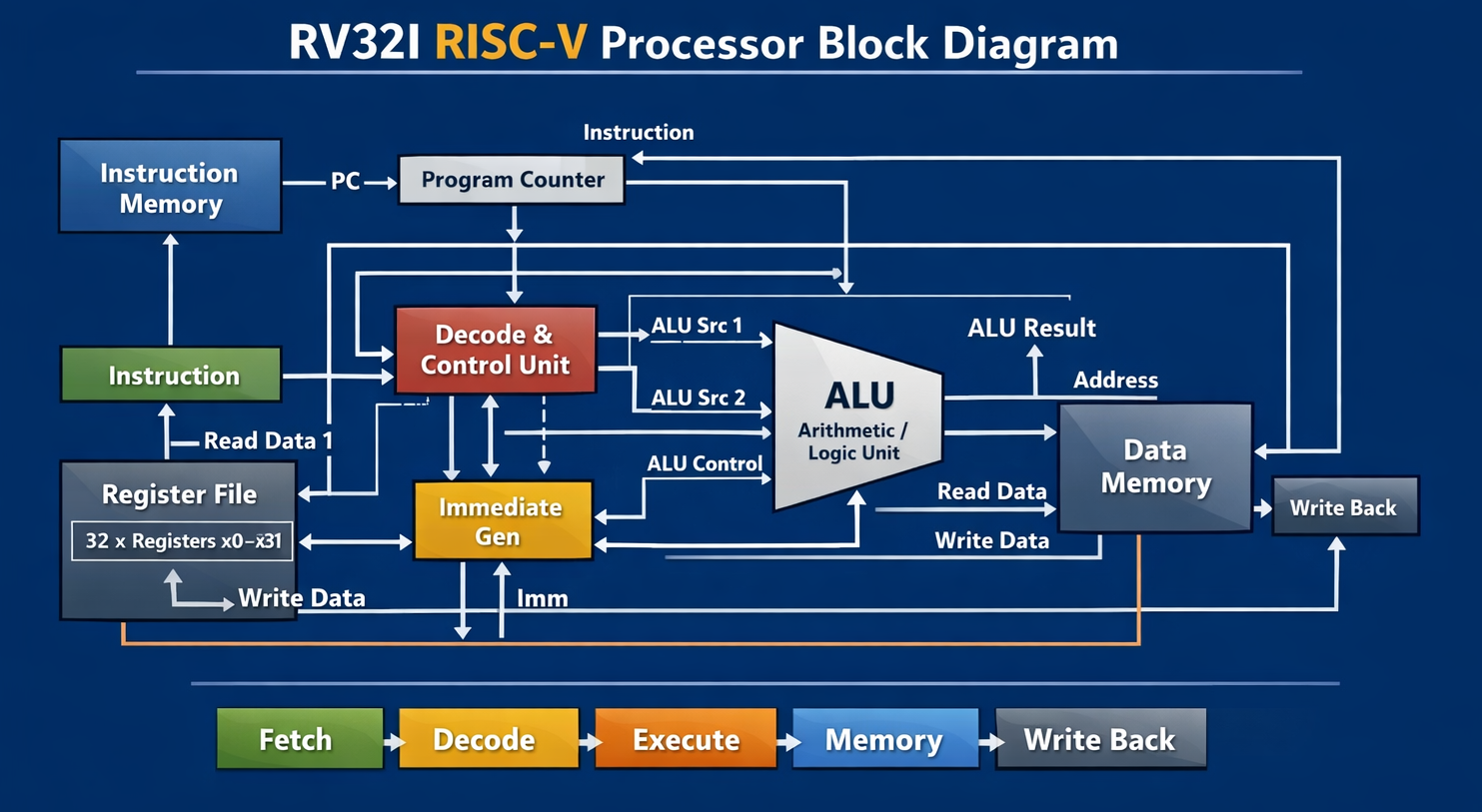

🔹 3. CPU Structure (RV32I Core)

A simple RV32I CPU has:

- Registers (32 total) →

x0tox31 - ALU → does math/logic

- Program Counter (PC) → tracks current instruction

- Memory interface → load/store data

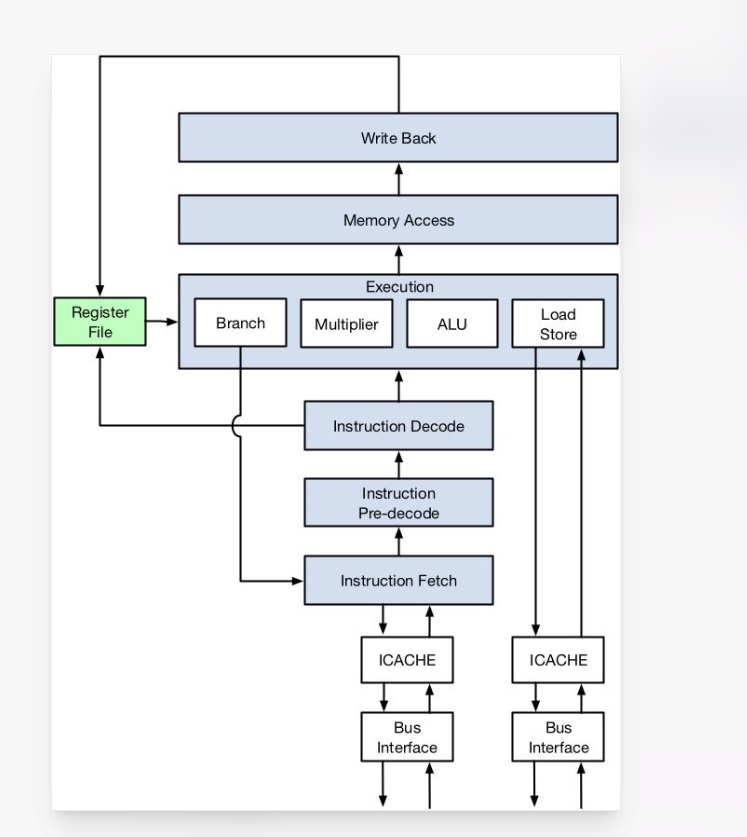

🔹 4. How It Works (Step-by-Step)

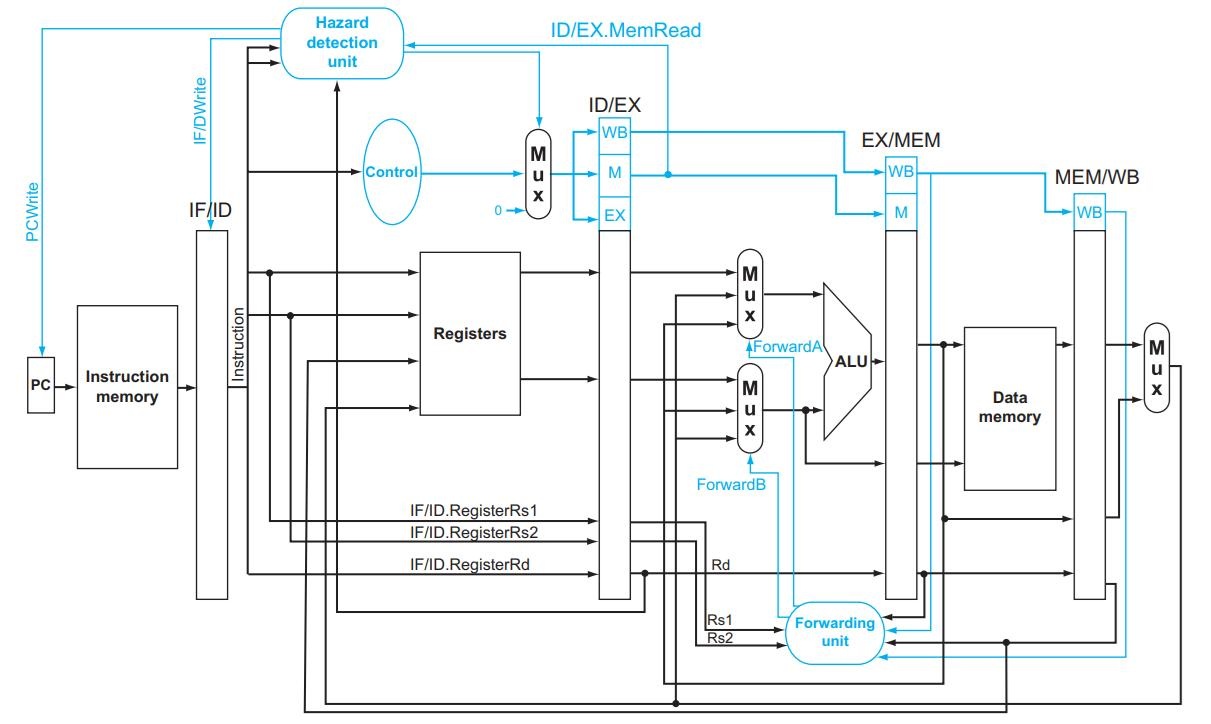

Every instruction follows this cycle:

🧭 1. Fetch

- CPU reads instruction from memory using PC

🔍 2. Decode

- Break instruction into parts:

- opcode

- registers

- immediate values

⚙️ 3. Execute

- ALU performs operation

(e.g., addition, comparison)

💾 4. Memory (if needed)

- Load/store data

✅ 5. Write Back

- Result stored into register

👉 This is the classic:

Fetch → Decode → Execute → Memory → Writeback

🔹 5. Example (Simple Instruction)

ADD x3, x1, x2

What happens:

- Read

x1andx2 - ALU adds them

- Store result in

x3

🔹 6. Why RV32I is Important

💡 1. Minimal but Complete

You can build a working CPU with just RV32I.

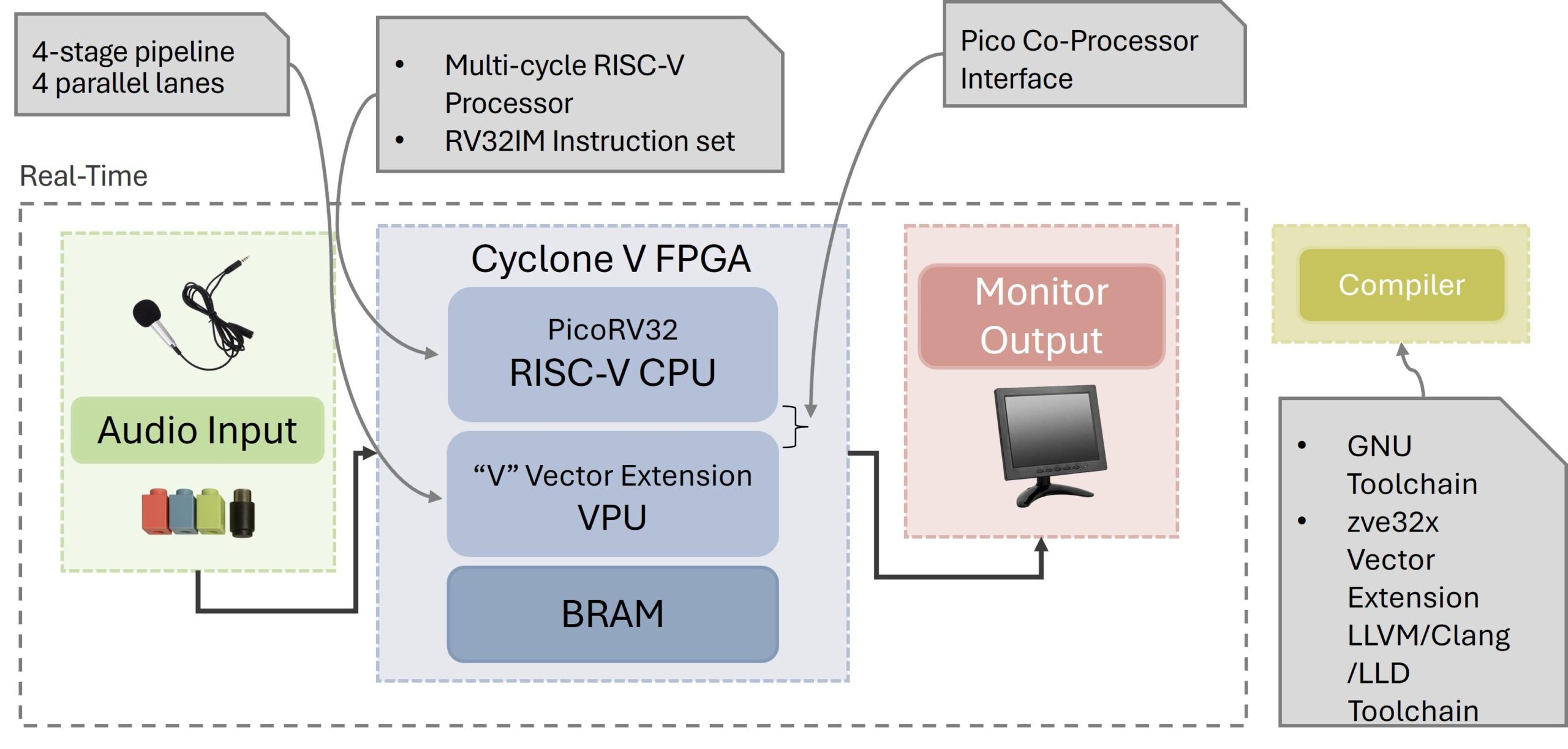

💡 2. Perfect for FPGA

Most beginner RISC-V FPGA projects use RV32I.

💡 3. Modular Design

You can extend it with:

- M → multiply/divide

- F → floating point

- C → compressed instructions

🔹 7. FPGA Perspective (This is where it gets real)

RV32I is not “code”.

It becomes:

- registers → flip-flops

- ALU → combinational logic

- control → state machines

👉 You are literally building a CPU in hardware.

🔥 Final Insight

- Python → tells computer what to do

- C → tells computer how to do it

- RV32I → defines what the CPU itself understands

And if you implement RV32I on FPGA…

👉 You’re not programming anymore.

👉 You’re designing the machine.