1.RISC-V Instruction Set Architecture Features

The RISC-V instruction set has standard 32-bit architecture as well as 64-bit and 128-bit architectures. The general-purpose registers in the 64-bit architecture are 64 bits, while those in the 128-bit architecture are 128 bits. The corresponding program counters (PCs) are also 64 bits and 128 bits, respectively.

The powerful 64-bit and 128-bit architectures of the RISC-V instruction set are aimed at mainstream personal computers (PCs), laptops, and servers, but they have not yet matured commercially, such as in embedded systems.

The development of multi-core systems and efficient advanced pipeline systems has made RISC-V-based systems a strong competitor to X86 and ARM systems.

The traditional approach to computer architecture is incremental instruction set, where new processors must not only implement new instruction set extensions, but also implement all past instruction sets to ensure backward compatibility.

The difference of X86 and ARM instruction set :

- X86 was invented in 1978 and on average, it adds about three instructions per month. This means that each update to X86 must include all previous extensions, whether they are practical instruction sets or ones that are obsolete or poorly designed. The downside to this approach is that the cost for users increases as the instruction set grows.

- The ARM architecture is divided into three series: A (application), R (real-time), and M (embedded), each of which has been optimized for specific use cases. These series do not have modular design features. On the other hand, X86 does not have modular characteristics.

1.1 The Core of RISC-V

The RISC-V instruction set adopts a modular architecture design, which can achieve a balance between cost, power consumption, performance, and other aspects.

The core of RISC-V includes:

- The basic instruction set of RV32I, which is fixed and will never change. This provides users and developers with a stable target.

- The modularity and composability of the RISC-V instruction set enable it to adapt to different design requirements. For example, if it is to be used as a digital signal processor (DSP), a multiplication and division module is needed for data processing, while the atomic instruction set may not be required. That is, other modules are optional and will not become burdensome if not used, thus avoiding a poor user experience.

- The module development of RISC-V will only be based on technological reasons and will be decided by the foundation. Even if new modules are added, users still have the right to choose whether to use them.

1.2 The Core Modules of Risc-V

The core of RISC-V consists of a series of standard modules, including:

- Core module: containing the basic instruction set, composed of 32-bit and 64-bit architecture.

- Extension module: can be used to expand the functionality of the core module, such as floating-point operations, vector operations, encryption and security extensions, etc.

- Mobile module: can compress 32-bit instructions into 16-bit instructions, which can reduce memory usage and power consumption.

- Privileged module: used to support operating systems and virtualization.

This modular design allows the RISC-V instruction set to be customized according to the specific needs of applications, and also provides more flexibility for future extensions.

2. RISC-V Instruction Set Classification

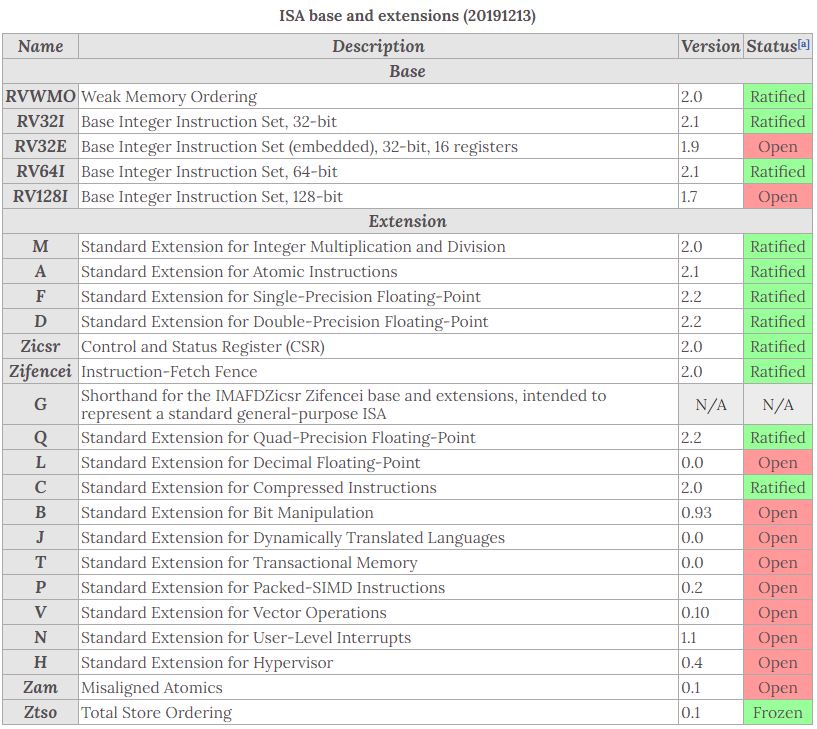

RISC-V is divided into subsets such as I, M, E, C, F, D, A, Q, L, and B, as shown in the following figure:

- Basic configuration subset consists of four types: RV32I, RV32E, RV64I, and RV128I.

- The Extension Subsets powerful RISC-V CPU architectures that extend the basic configuration subsets. These subsets are composed of combinations of M, C, F, D, A, Q, L, B, etc.

- The convention for extension subsets is to directly add them to the name of the basic subset as an indicator.

- adding single-precision floating-point extension operations and atomic instructions to RV32I, it becomes RV32IFA. RV32I is a 32-bit standard integer instruction set, and is also the most basic instruction set. It can implement a complete software and hardware system and is a mandatory part of the instruction set. It can be used in a wide range of embedded systems (RV32I).

- The combination of instruction sets I, M, A, F, D, and C is also called “general” combination, represented by the English letter G, namely RV32G. The RISC-V instruction set can be low-power and low-cost, such as the ultra-low-power and ultra-low-cost basic instruction set RV32E, and the standard extended instruction set RV32IC (similar to ARM Thumb). The RV32IC instruction set can compress code density to 30%-40%, thus saving code space in memory.

The Version numbers in Figure 1 are defined by the non-privileged instruction set (early user-level instruction set) released by RISC-V. The latest version, 2.2, was released on December 13, 2019, and updates include F, D, and Q. Other instruction sets remain at previous versions, such as version 2.1. The Status section shows whether the instruction sets have been officially released or are still in development (Open). Frozen indicates that the module will not undergo significant changes before being submitted for approval.

The Table format of Figure 1

By default, only the core ISA must be implemented presenting great opportunity for area and energy optimization. However, additional functionality is sometimes desired. RISC-V comes with a series of standard extensions that enable additional functionality beyond the core ISA such as floating point and operations and bit manipulation.

Extensions can be implemented and omitted as desired. Those extensions are:

| Name | Description | Version | Status | Instruction Count |

|---|---|---|---|---|

| RV32I | Base Integer Instruction Set – 32-bit | 2.1 | Frozen | 49 |

| RV32E | Base Integer Instruction Set (embedded) – 32-bit, 16 registers | 1.9 | Open | Same as RV32I |

| RV64I | Base Integer Instruction Set – 64-bit | 2.0 | Frozen | 14 |

| RV128I | Base Integer Instruction Set – 128-bit | 1.7 | Open | 14 |

| Extension | ||||

| M | Standard Extension for Integer Multiplication and Division | 2.0 | Frozen | 8 |

| A | Standard Extension for Atomic Instructions | 2.0 | Frozen | 11 |

| F | Standard Extension for Single-Precision Floating-Point | 2.0 | Frozen | 25 |

| D | Standard Extension for Double-Precision Floating-Point | 2.0 | Frozen | 25 |

| G | Shorthand for the base and above extensions | n/a | n/a | n/a |

| Q | Standard Extension for Quad-Precision Floating-Point | 2.0 | Frozen | 27 |

| L | Standard Extension for Decimal Floating-Point | 0.0 | Open | Undefined Yet |

| C | Standard Extension for Compressed Instructions | 2.0 | Frozen | 36 |

| B | Standard Extension for Bit Manipulation | 0.90 | Open | 42 |

| J | Standard Extension for Dynamically Translated Languages | 0.0 | Open | Undefined Yet |

| T | Standard Extension for Transactional Memory | 0.0 | Open | Undefined Yet |

| P | Standard Extension for Packed-SIMD Instructions | 0.1 | Open | Undefined Yet |

| V | Standard Extension for Vector Operations | 0.7 | Open | 186 |

| N | Standard Extension for User-Level Interrupts | 1.1 | Open | 3 |

| H | Standard Extension for Hypervisor | 0.0 | Open | 2 |

| S | Standard Extension for Supervisor-level Instructions | 1.12 | Open | 7 |