Here’s a practical, no-fluff RV32I FPGA implementation roadmap — focused on getting you from zero → running code on hardware.

hase 0 — Setup (1 day)

Goal: Write Verilog, simulate, and compile RISC-V code

- FPGA tools:

- Vivado (Xilinx)

- Quartus (Intel)

- Simulation:

- ModelSim or Verilator

- Toolchain:

- riscv-gnu-toolchain

👉 Output:

.c → .elf → .hexworking

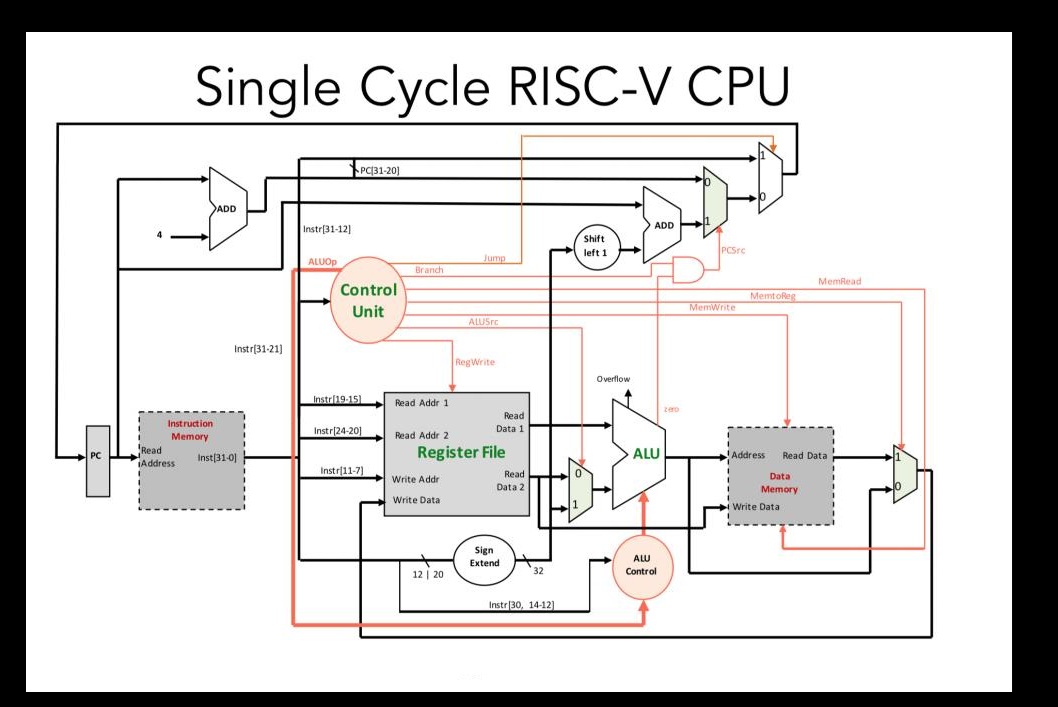

Phase 1 — Single-Cycle CPU (3–5 days)

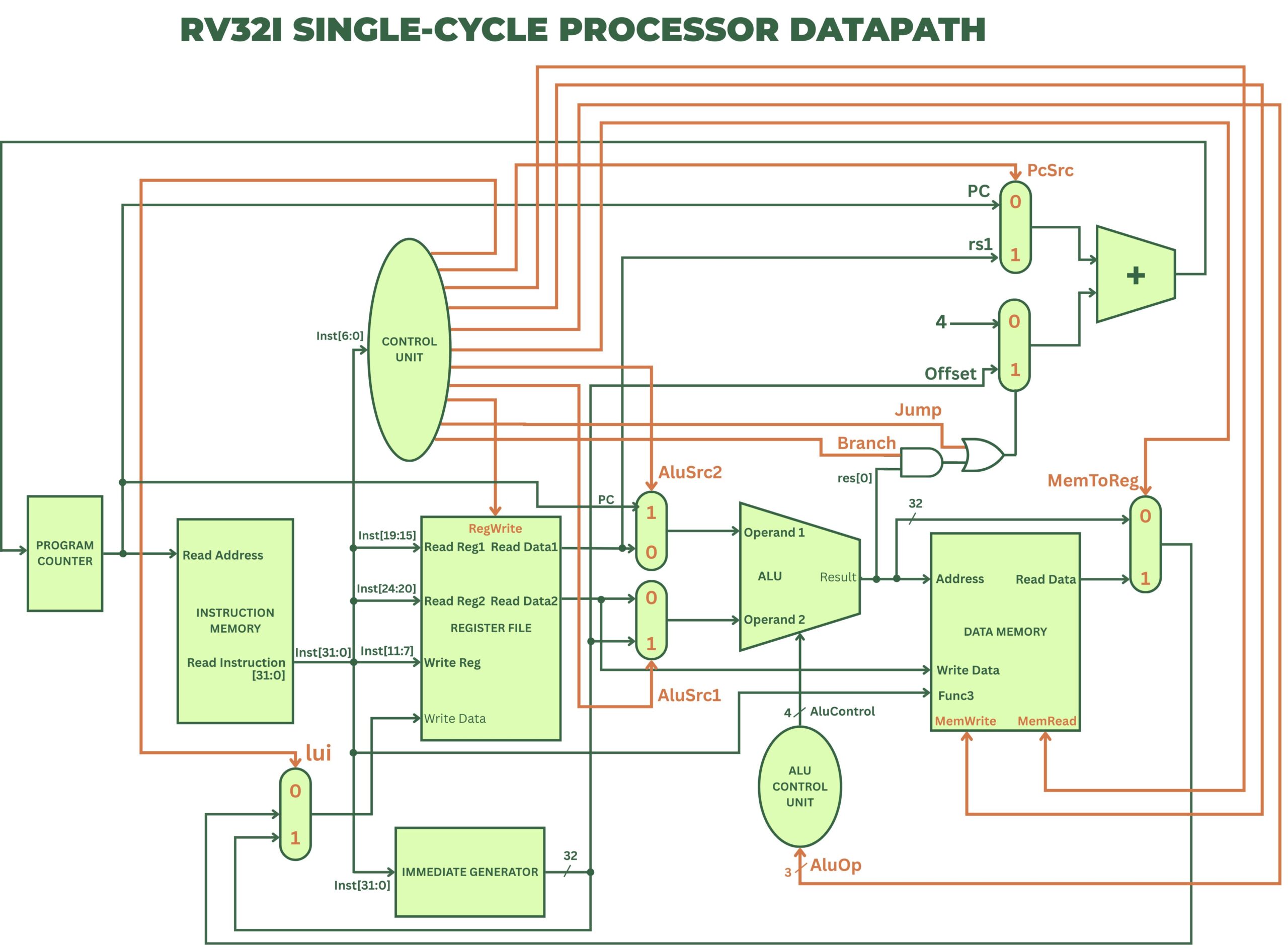

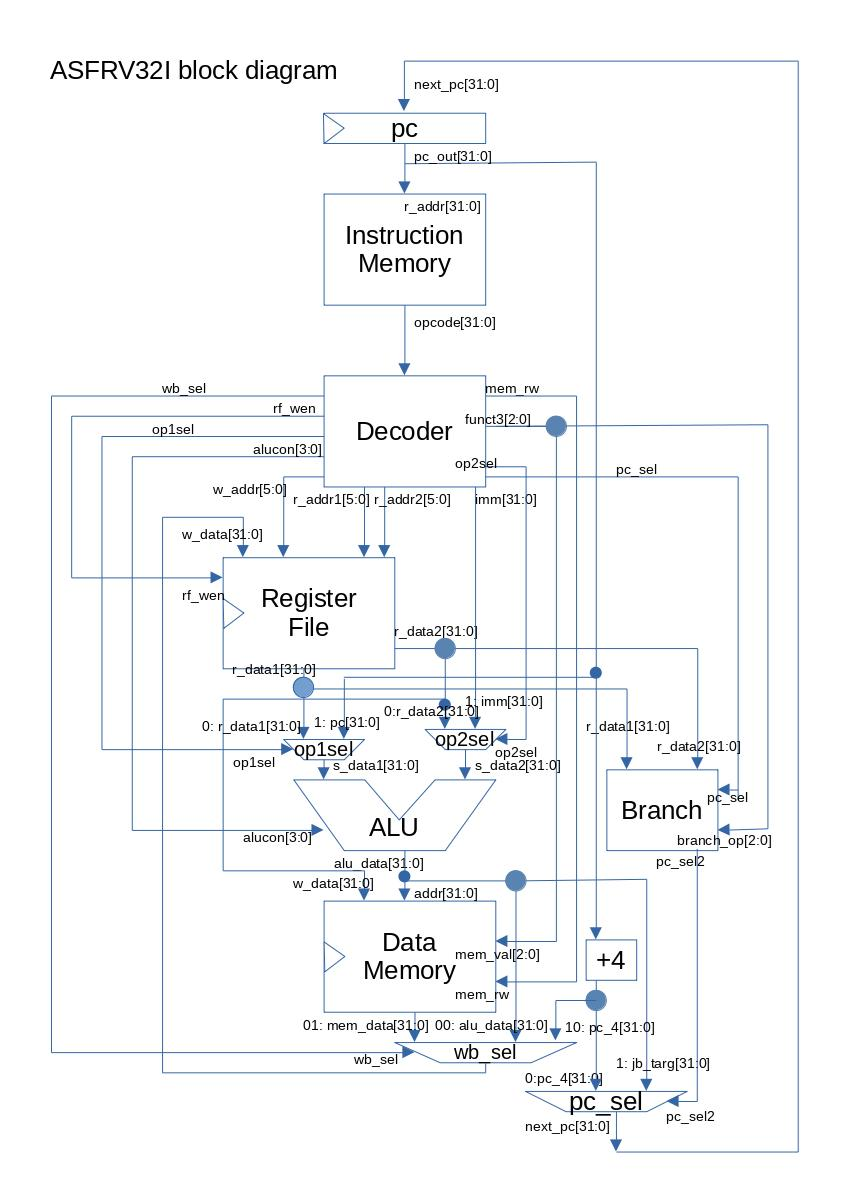

Build the minimum working CPU

Modules:

- PC (Program Counter)

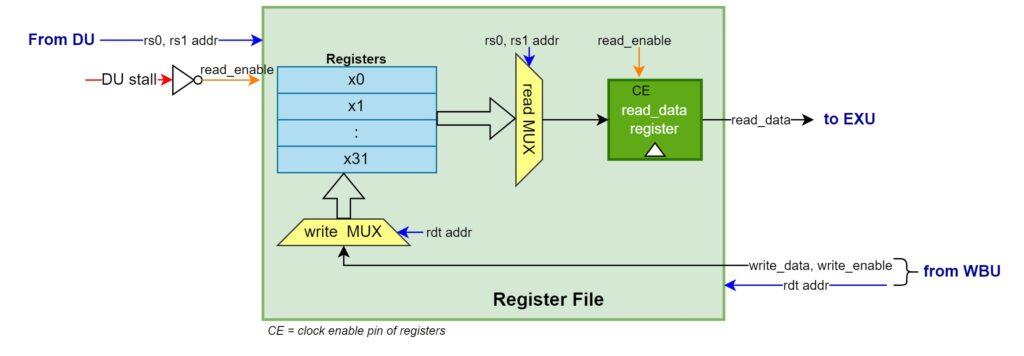

- Register File (32 registers)

- ALU (ADD/SUB/AND/OR)

- Instruction Memory (ROM)

- Data Memory (RAM)

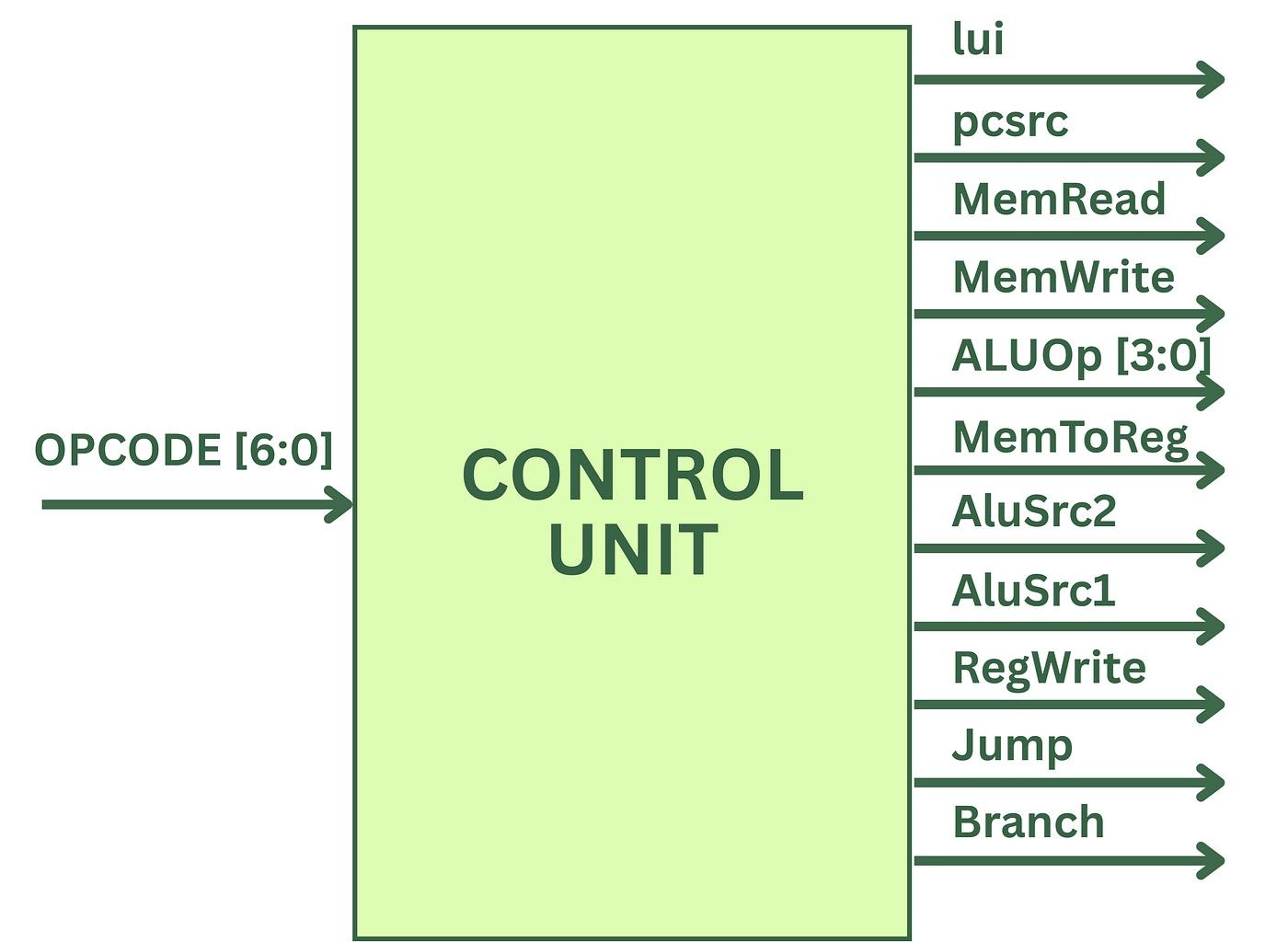

- Control Unit

Minimum instructions:

ADD,SUBADDILW,SWBEQJAL

👉 Test goal:

int a = 1 + 2;

If this runs → you have a working CPU.

Phase 2 — Expand RV32I (3–7 days)

Add more instructions

- Logic:

XOR,SLL,SRL - Compare:

SLT,SLTU - Branch:

BNE,BLT

Key challenges:

- Immediate decoding (VERY error-prone)

- Branch offset calculation

👉 Goal:

- Run loops and simple

if/else

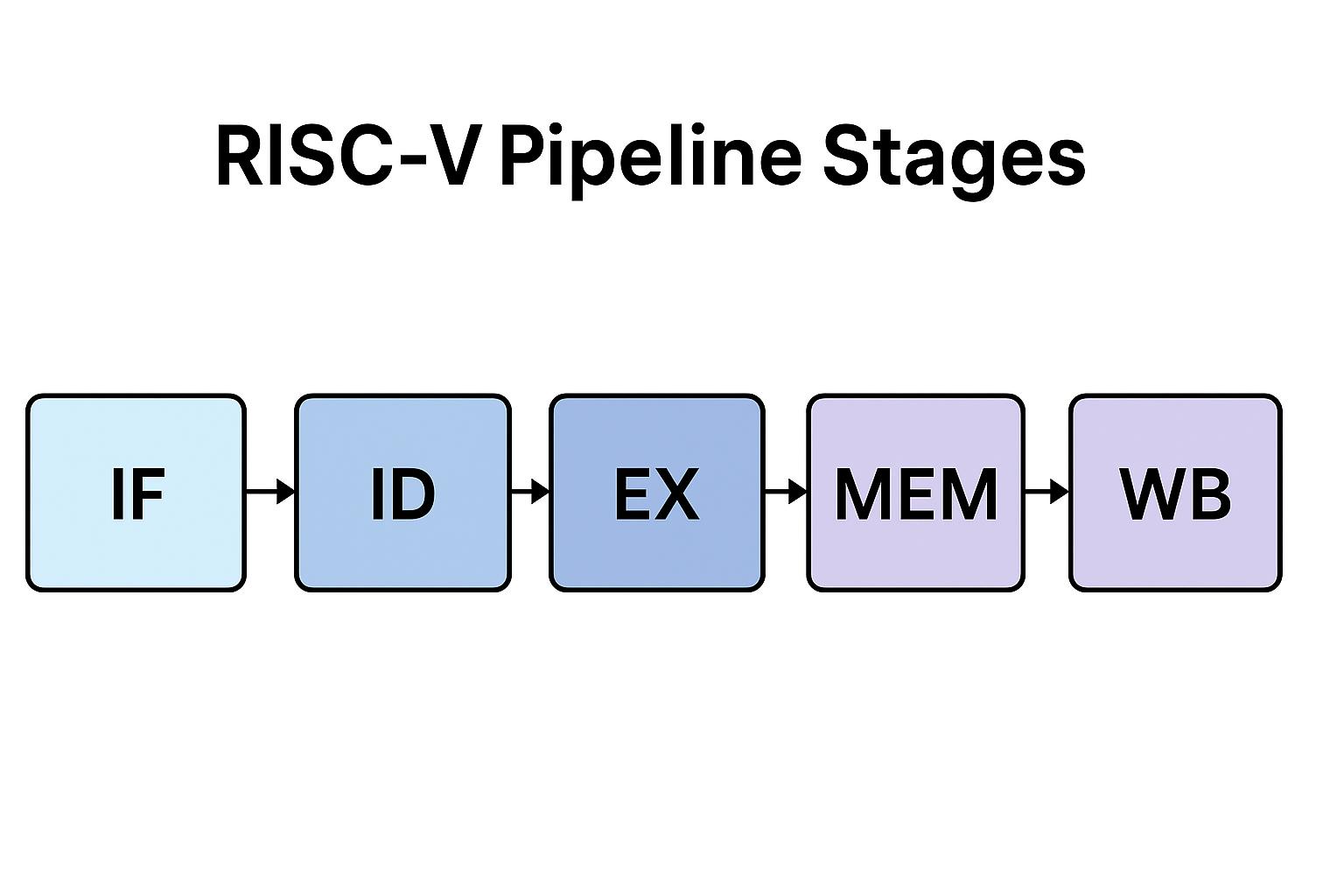

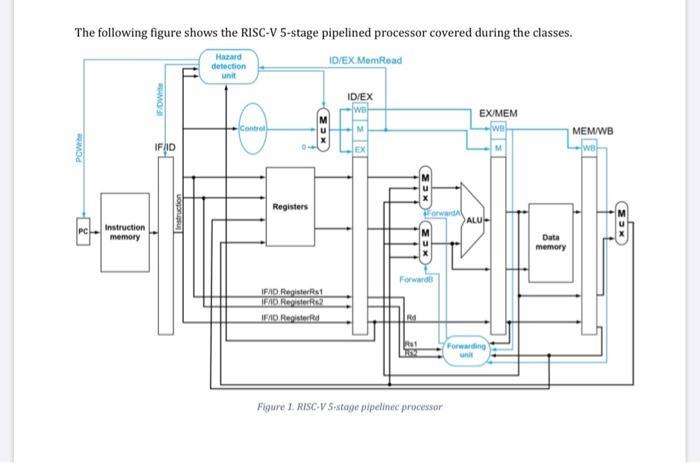

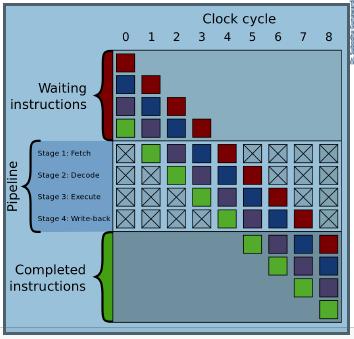

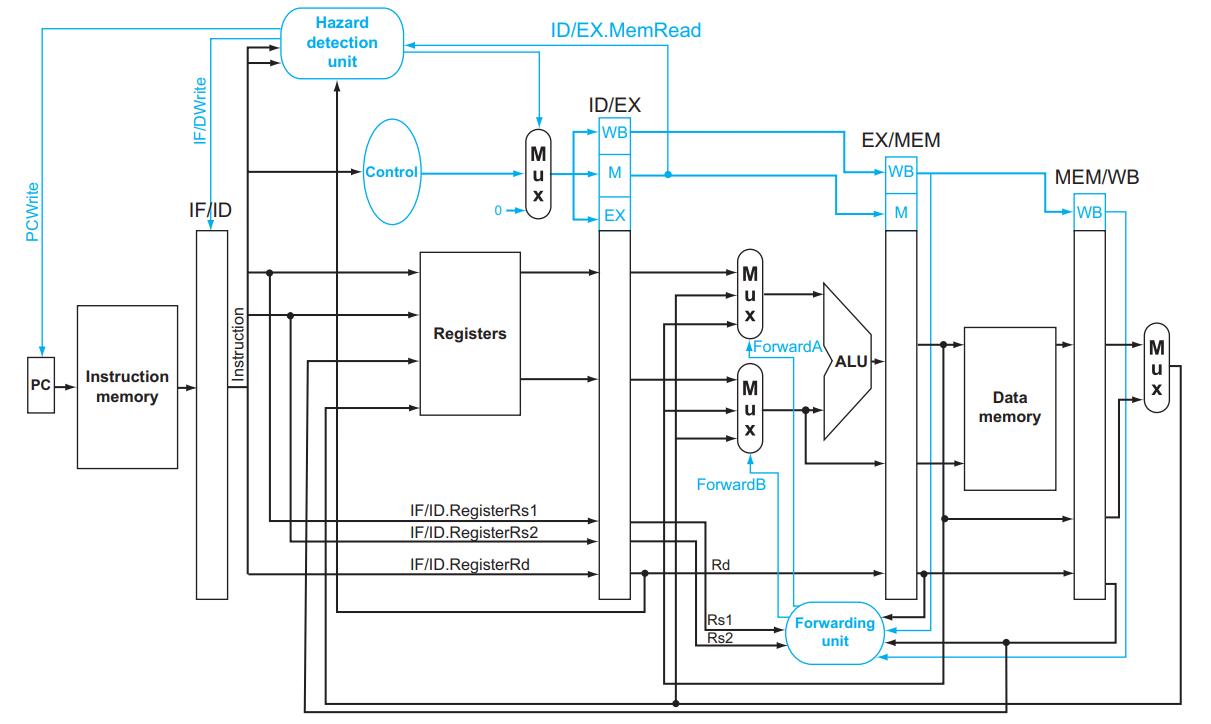

Phase 3 — Pipeline (5–10 days) 🔥

Move from single-cycle → 5-stage pipeline

- IF (Fetch)

- ID (Decode)

- EX (Execute)

- MEM

- WB (Write Back)

Add:

- Pipeline registers (IF/ID, ID/EX…)

- Hazard detection

- Forwarding (bypass)

Hard parts:

- Data hazards

- Control hazards (branches)

👉 Result:

- Multiple instructions running in parallel

Phase 4 — Simulation & Verification (ongoing)

- Write testbenches

- Compare against software results

- Use official tests:

- RISC-V ISA tests

👉 Goal:

- No silent bugs (this matters more than features)

🔌 Phase 5 — Run on FPGA (2–3 days)

Hook up real hardware

- Clock

- Reset

- UART (for output)

👉 Example:

printf("Hello RISC-V");

If you see serial output → you made it 🎉

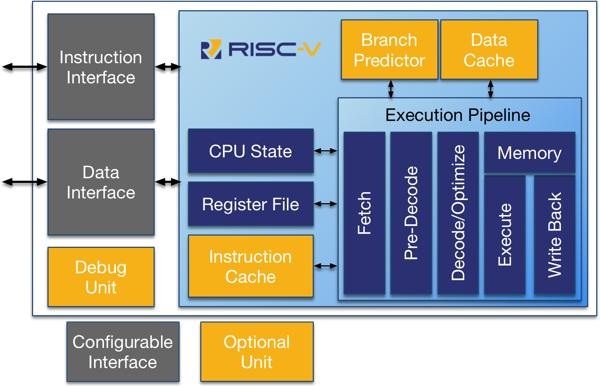

⚡ Phase 6 — Advanced (optional)

- Cache (I/D cache)

- Branch predictor

- M-extension (mul/div)

- Simple OS / RTOS

🧠 What You’re Really Doing

You are NOT “writing code”.

You are designing:

- Datapath (how data flows)

- Control logic (what happens when)

- Timing (when it happens)