🎬 Video Script: The Reinvention of the CPU — And the 50-Year War Between CISC and RISC In recent years, tech headlines have been dominated…

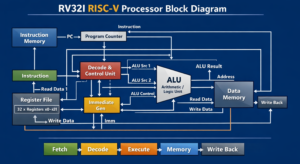

================================================== 1. Registers Registers are tiny, very fast storage locations inside the CPU. RV32I has 32 integer registers: Each register is 32 bits wide. You…

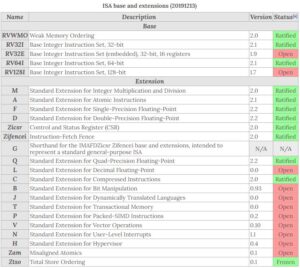

1. What is RISC-V? RISC-V is an Instruction Set Architecture (ISA). An ISA is the rulebook that defines: RISC-V is special because it is: RISC…

— here’s a clear, no-BS PicoRV32 tutorial to get you from “what is this” → “I can run it on FPGA / simulate it”. 🧠…

Here’s a practical, no-fluff RV32I FPGA implementation roadmap — focused on getting you from zero → running code on hardware. hase 0 — Setup (1…

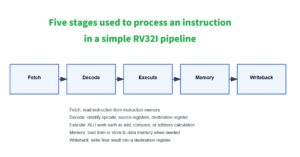

🔹 1. What is RV32I? RV32I is the base instruction set of the RISC-V architecture. RV = RISC-V 32 = 32-bit (registers are 32 bits…

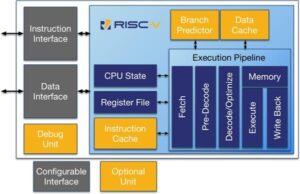

Full Beginner Guide: How to Build a RISC-V CPU on an FPGA (2026 Edition) Building a RISC-V CPU on an FPGA is one of the…

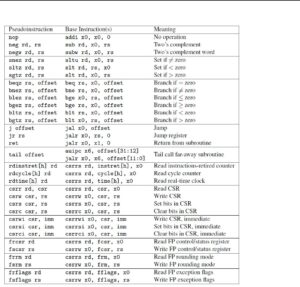

RISC-V Pseudo-Instruction Lookup Table Assembler Pseudo-instructions The assembler implements a number of convenience psuedo-instructions that are formed from instructions in the base ISA, but have…

This article will start with the I-Type integer register instructions and provide a detailed introduction to each assembly instruction and its specific implementation. 1. I-type…

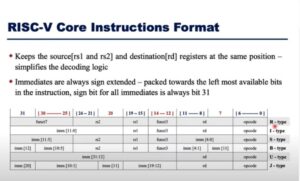

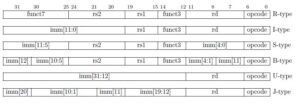

1.RISC-V Introduction the Origin of RISC-V, and the Features of RISC-V RISC-V Instruction Set Architecture Features and Classification RISC-V Instruction Set Encoding Structure, Features and…

1.RISC-V Instruction Set Explanation RISC-V is an open and free instruction set architecture widely used in processors and embedded systems. The RISC-V instruction set follows…

1.RISC-V Instruction Set Architecture Features The RISC-V instruction set has standard 32-bit architecture as well as 64-bit and 128-bit architectures. The general-purpose registers in the…

RISC-V is an open-source instruction set architecture (ISA) that was originally developed at the University of California, Berkeley in 2010. The project was led by…