🧠 RV32I vs PicoRV32 — Visual Diagrams (Deep Mapping)

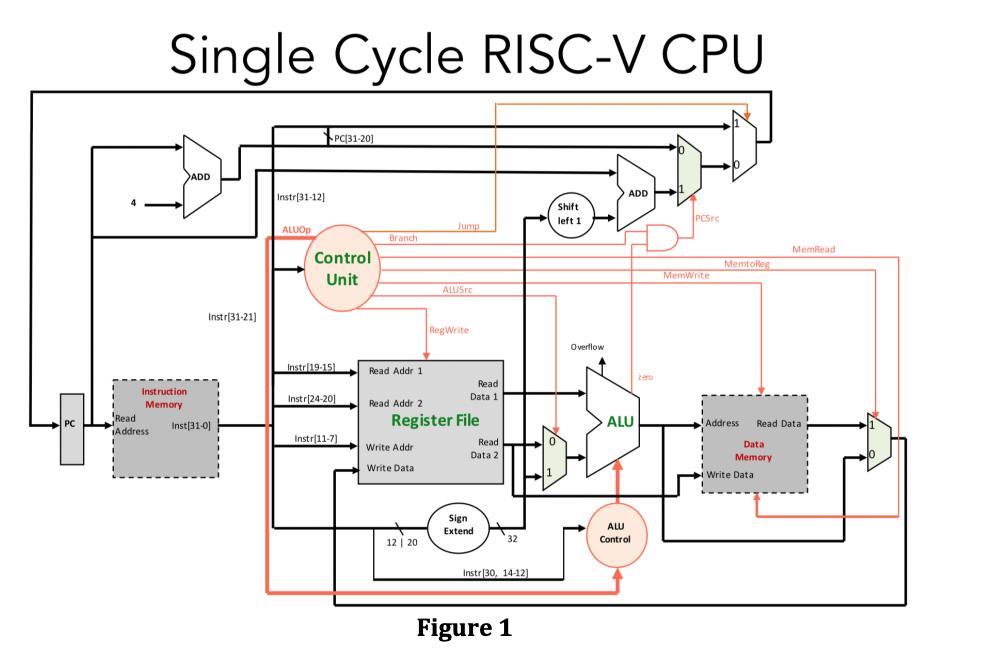

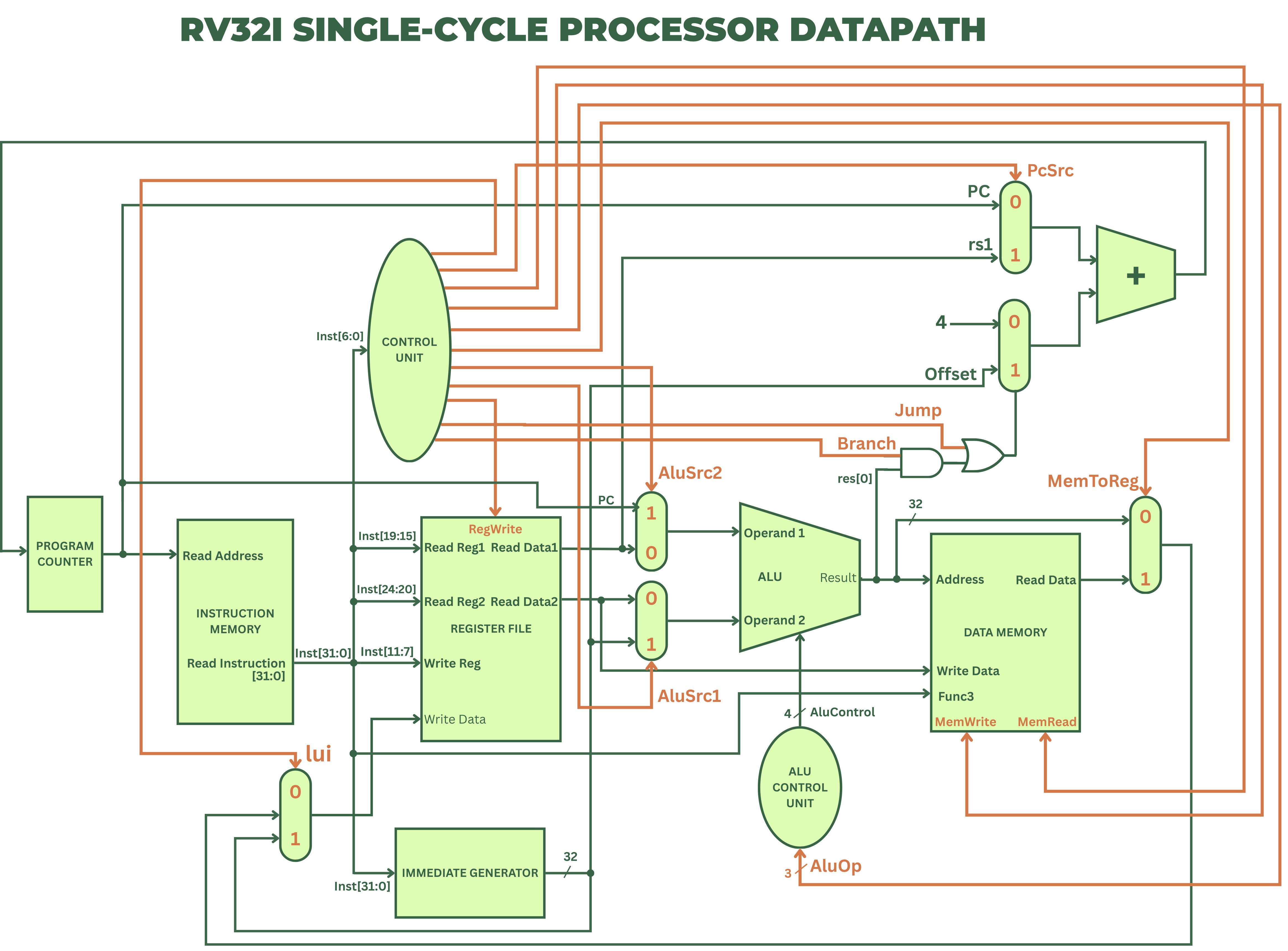

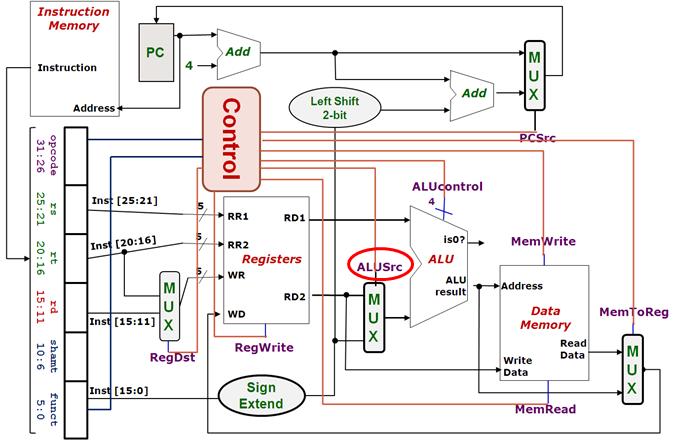

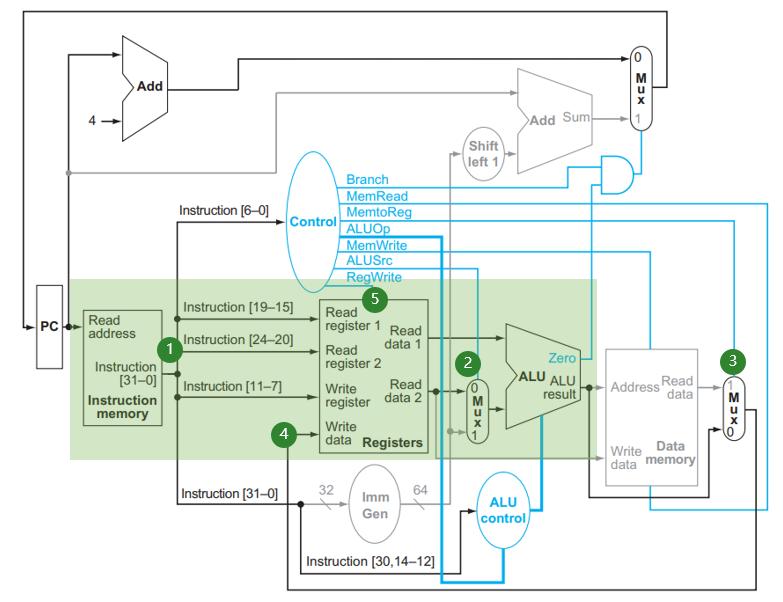

🟣 1. RV32I Single-Cycle (Your Diagram Style)

🔎 How to read it:

- Everything happens in parallel

- Clear split:

- Controller → generates signals

- Datapath → executes

- Signals like:

ALUControl,RegWrite,PCSrc

👉 Think:

“All hardware active at once”

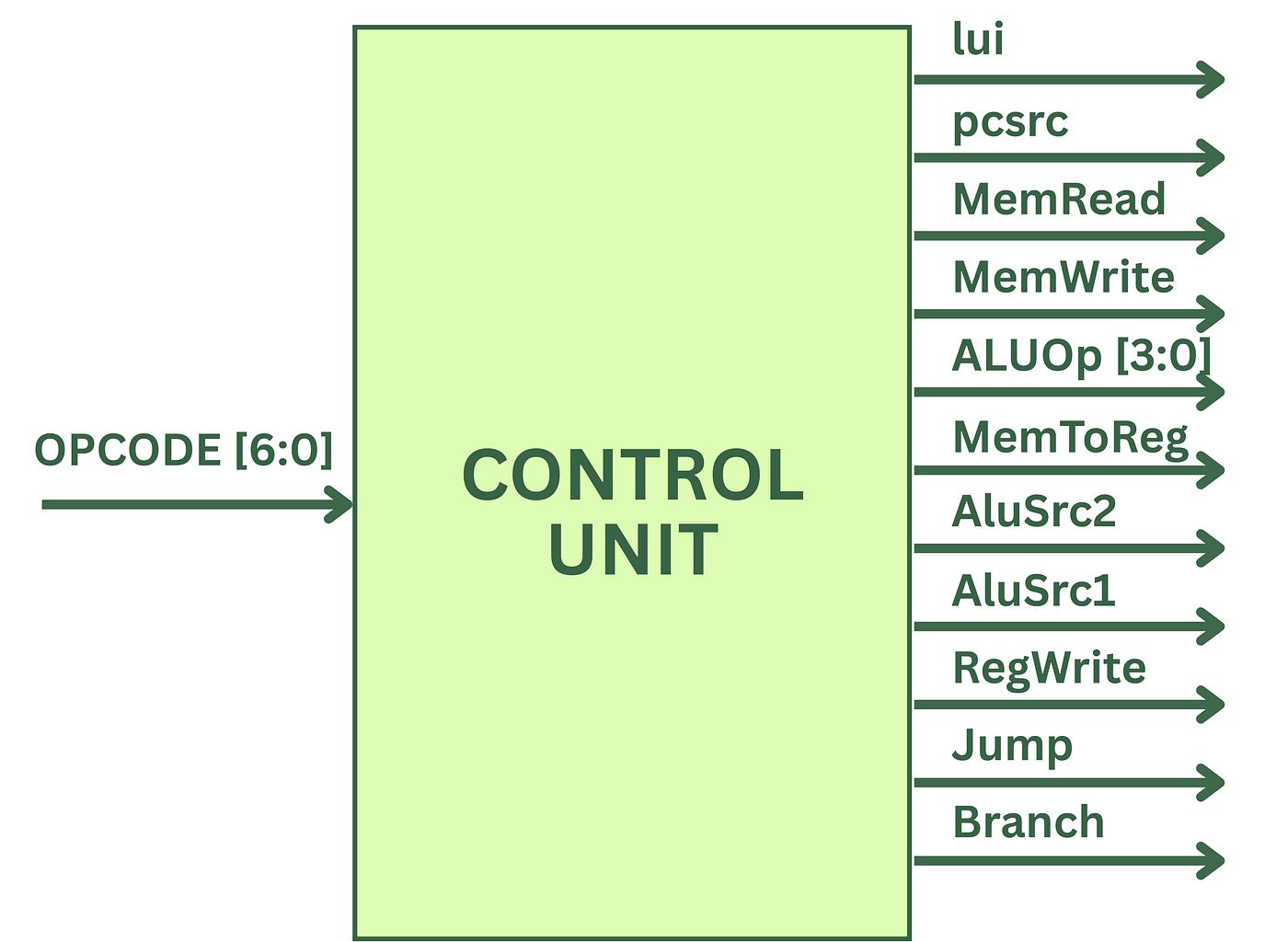

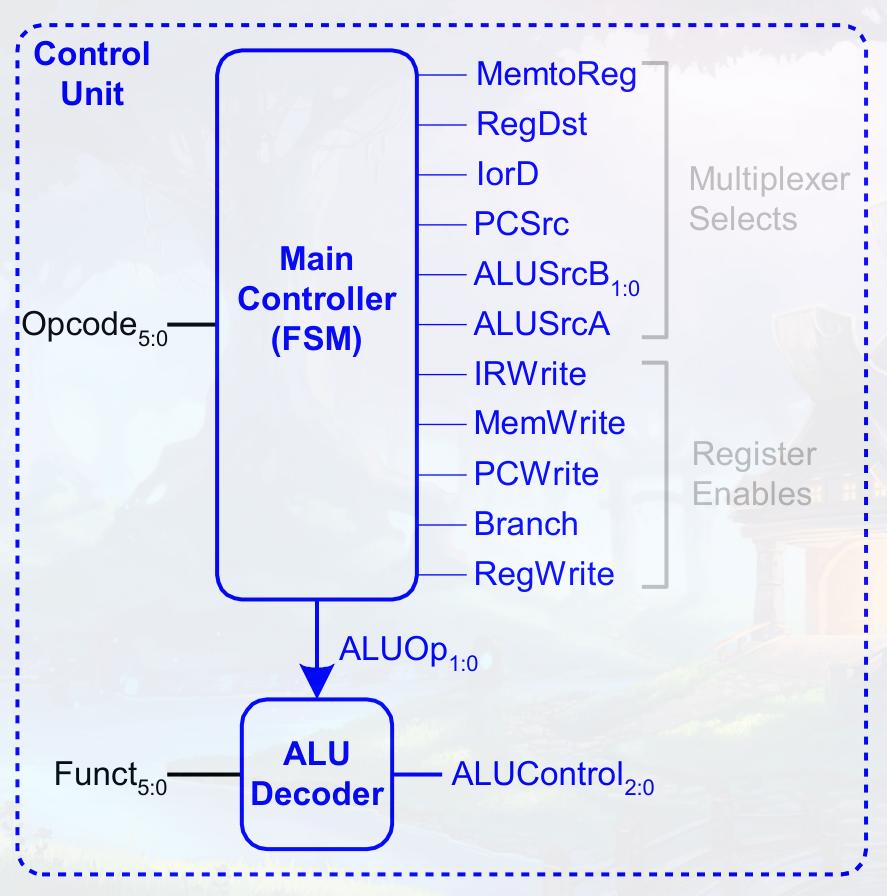

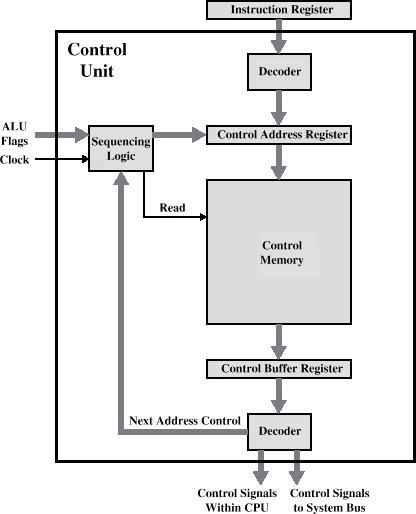

🟢 2. PicoRV32 (FSM-Based Architecture)

🔎 How to read it:

- No clean controller/datapath split

- One central:

- FSM (state machine)

- Hardware reused:

- ALU

- Registers

- Memory interface

👉 Think:

“One block doing different things over time”

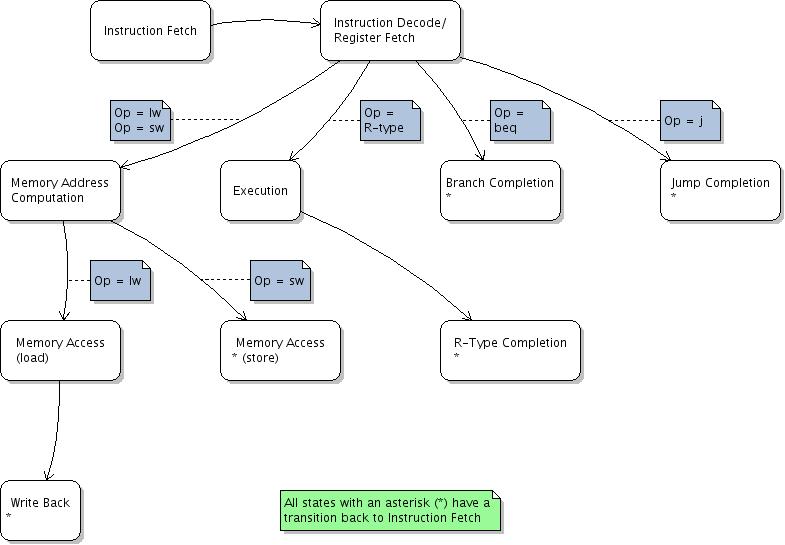

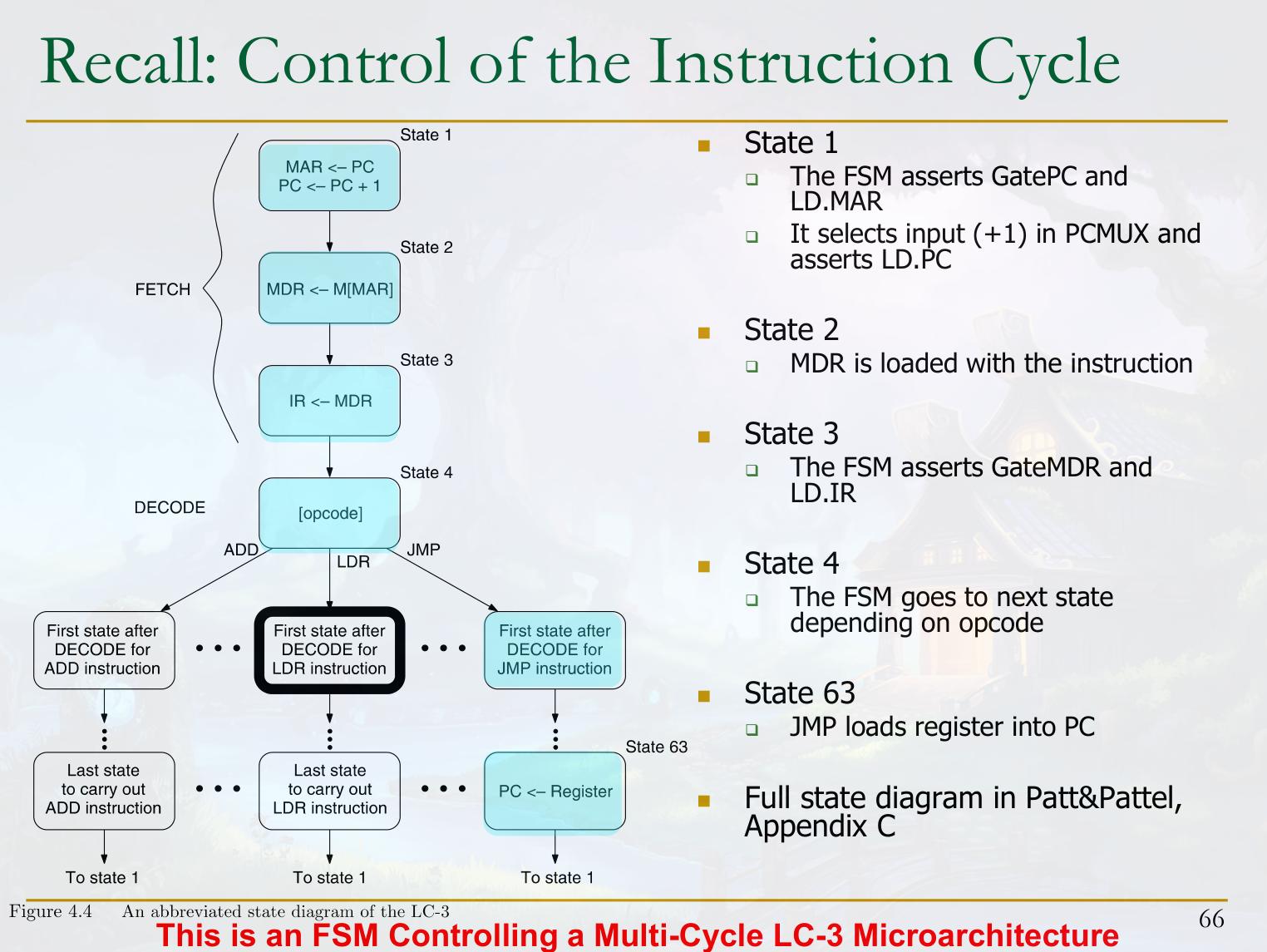

🔄 3. The KEY Mapping (Visual Insight)

🧠 Parallel → Sequential Transformation

RV32I (space) PicoRV32 (time)

[ALU] Cycle 3 → use ALU

[RegFile] ------→ Cycle 2 → read regs

[Memory] Cycle 4 → access memory

[Control] FSM decides each step

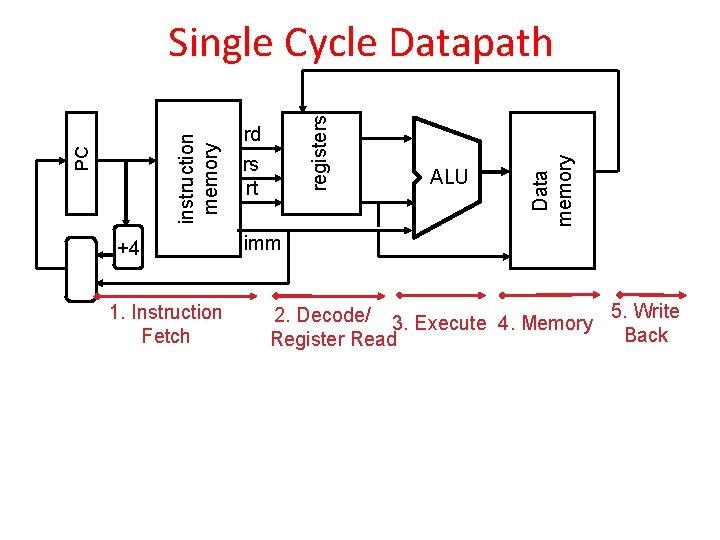

⏱️ 4. Execution Timeline Comparison

🟣 RV32I (Single Cycle)

[ FETCH | DECODE | EXECUTE | MEM | WB ] ← 1 clock

🟢 PicoRV32 (Multi-Cycle FSM)

Cycle 1: FETCH

Cycle 2: DECODE

Cycle 3: EXECUTE

Cycle 4: MEMORY

Cycle 5: WRITEBACK

🎯 5. Side-by-Side Mental Model

RV32I:

┌───────────────┐

│ Everything NOW│

└───────────────┘

PicoRV32:

┌───────────────┐

│ Step-by-step │

│ reuse hardware│

└───────────────┘

🔥 One Diagram to Remember

👉 This is the whole story:

RV32I diagram

↓ (fold over time)

PicoRV32 FSM

⚡ If you want next-level diagrams

I can draw for you:

- 🔍 ADD instruction: signal-level flow vs FSM cycles

- 📉 Waveform-style timing diagram

- 🧩 Exact mapping to picorv32.v code blocks

Just tell me 👍