This article will continue to introduce the remaining integer register-immediate instructions in the I-type (here it is the shift instruction).

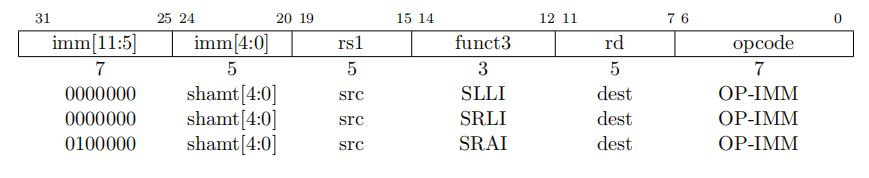

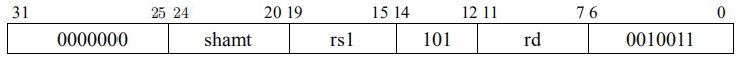

Figure 1 shows a shift instruction with an immediate value for the number of shifts. Other shift instructions will be introduced later. From the machine code format, it can be seen that these three instructions are somewhat different from the six I-type instructions mentioned earlier in the text. The I-immediate in this article is divided into two parts.

shamt – shift amount

The imm[10] (bit 30 of the machine code) in imm[11:5] is used to differentiate between the types of shifts. The SLLI and SRLI instructions have a value of 0 for bit 30, while the SRAI instruction has a value of 1 for bit 30 of the machine code.

1.1. SLLI

Shift Left Logical Immediate

Instruction Format:

SLLI rd,rs1,shamt x[rd] = x[rs1] ≪ shamt

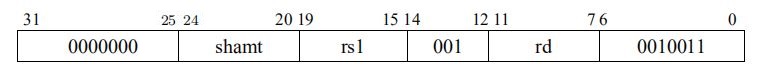

The machine code is shown in Figure 2, with OP-IMM for SLLI being 001_0011, funct3 being 001, and IMM[10] being 0.

The number of bits to shift is determined by imm[4:0]. This instruction left-shifts the value in rs1 by shamt[4:0] bits, with zeroes filled in for the lower bits of rs1, and the result is written to rd.

1.1.1 Example

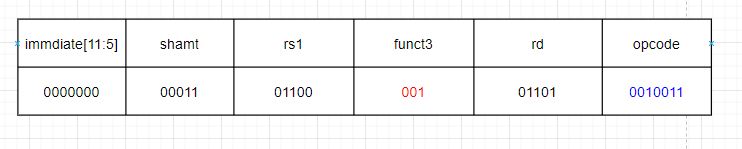

SLLI x13,x12,3

Left shift the value in register x12 by 3 bits and write the result to register x13.

- OP-IMM: 001_0011

- funct3: 001

- shamt: 5’b0_0011

- bit 25-31: 7’b000_0000

- rs1: 5’b0_1100

- rd: 5’b0_1101

SLLI x13,x12,3machine code:

0000000_00011_01100_001_01101_0010011 .

The corresponding hexadecimal representation is 0x0036_1693 in 32-bit format.

1.2. SRLI

Shift Right Logical Immediate

Instruction Format:

SRLI rd,rs1,shamt。x[rd] = x[rs1] ≫𝑢 shamt

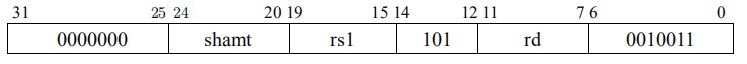

The machine code for the SRLI instruction with OP-IMM = 0010011, funct3 = 101, rd, rs1, and shamt[4:0] specified according to the given parameters is shown in Figure 3.

The SRLI instruction performs a logical right shift on the value in register rs1 by shamt[4:0] bits, filling the vacated bits with zeroes, and stores the result in register rd.

1.2.1 Example

SRLI x13,x12,5

Perform a logical right shift on the value in register x12 by 5 bits, fill the vacated bits with zeroes, and store the result in register x13

The OP-IMM and funct3 fields of the SRLI and SRAI instructions have the same encoding.

1.3. SRAI

Shift Right Arithmetic Immediate

Instruction Format:

SRAI rd,rs1,shamt。x[rd] = x[rs1] ≫𝑠 shamt

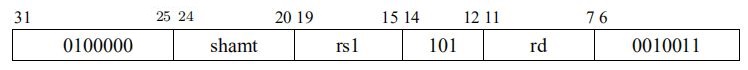

The SRAI instruction’s machine code is shown in Figure 4. It has an OP-IMM field of 001_0011, a funct3 field of 101, and an IMM[10] value of 1. The instruction performs an arithmetic right shift on the value in register rs1 by shamt[4:0] bits, filling the vacated bits with the value of rs1[31] (the sign bit), and stores the result in register rd.

1.3.1 Example

SRAI x13,x12,3

Perform an arithmetic right shift of 3 bits on the value in register x12 and store the result in register x13.

1.3.2 Please Note:

The difference between the two instructions is determined by the value of imm[10]:

- If imm[10] is 0, the instruction is SRLI (Shift Right Logical Immediate), which performs a logical right shift and fills the vacated bits with zeroes.

- If imm[10] is 1, the instruction is SRAI (Shift Right Arithmetic Immediate), which performs an arithmetic right shift and fills the vacated bits with the sign bit (the leftmost bit).

Both instructions shift the value in the specified register by the immediate value specified in shamt[4:0] and write the result to the specified destination register.

1.4 Example to Distinguish Between Arithmetic Right Shift and Logical Right Shift

Distinguish between arithmetic right shift and logical right shift, for example, for the binary number 1100_1100 (explained here using 8-bit numbers, but in RV32I the numbers stored in registers are 32-bit).

Shifting the binary number 1100_1100 by 3 bits to the right using arithmetic right shift gives the result 1111_1001.

Similarly, shifting the binary number 0011_0011 by 3 bits to the right using arithmetic right shift gives the result 0000_0110.

On the other hand, shifting 1100_1100 by 3 bits to the right using logical right shift gives the result 0001_1001.

Similarly, shifting 0011_0011 by 3 bits to the right using logical right shift gives the result 0000_0110.