1. What is RISC-V?

RISC-V is an Instruction Set Architecture (ISA).

An ISA is the rulebook that defines:

- what instructions the CPU understands

- how registers behave

- how memory is accessed

- how programs control execution

RISC-V is special because it is:

- open standard

- modular

- simple to learn

- widely used in teaching, research, and embedded systems

RISC means Reduced Instruction Set Computer.

The idea is to use a smaller set of simpler instructions instead of a very large and complicated instruction set.

2. What does RV32I mean?

RV32I breaks into three parts:

- RV = RISC-V

- 32 = 32-bit architecture

- I = base integer instruction set

So RV32I means:

- registers are 32 bits wide

- addresses and data paths are designed around 32-bit operation

- only the base integer instructions are included

RV32I does NOT include:

- multiplication/division extension (M)

- atomic instructions (A)

- floating point (F, D)

- compressed instructions (C)

That makes RV32I a very good starting point.

==================================================

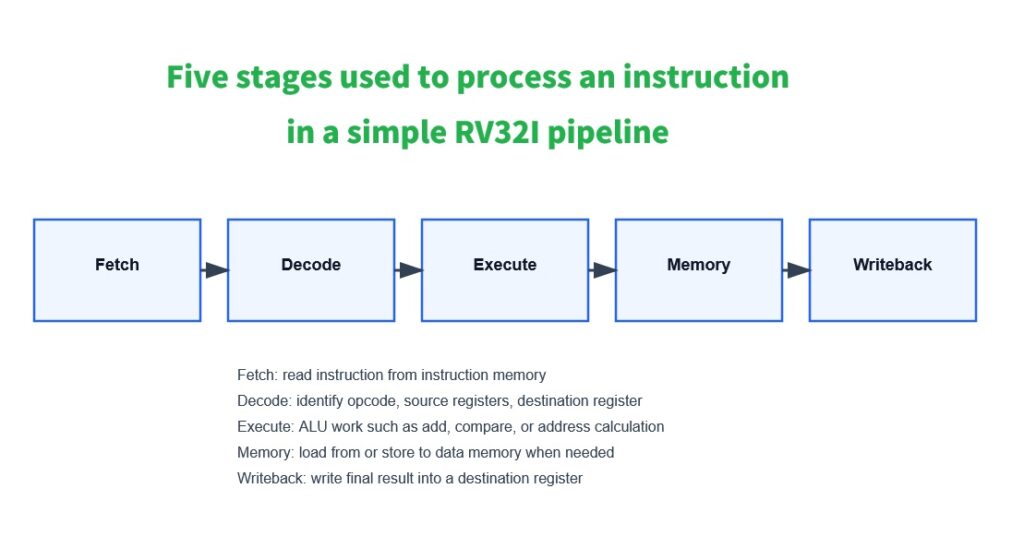

3. Big Picture: How a CPU Executes a Program

A simple model is:

+-----------+ +-----------+ +-----------+ | Fetch | ---> | Decode | ---> | Execute | +-----------+ +-----------+ +-----------+

More detail:

- Fetch

The CPU reads an instruction from memory using the Program Counter (PC). - Decode

The CPU figures out what the instruction means:

- which registers are used

- whether there is an immediate value

- what operation to perform

- Execute

The CPU performs the operation:

- add numbers

- compare values

- read or write memory

- jump to another instruction

- Write back

Many instructions write a result back to a register.

4. Program Counter (PC)

The Program Counter holds the address of the current instruction.

In RV32I:

- each instruction is 32 bits = 4 bytes

- the PC usually increases by 4 after each instruction

Example:

Address Instruction

0x0000 addi x1, x0, 5

0x0004 addi x2, x0, 10

0x0008 add x3, x1, x2

Execution flow:

PC=0x0000 -> execute first instruction

PC=0x0004 -> execute second instruction

PC=0x0008 -> execute third instruction

If a branch or jump happens, the PC may change to another address instead of PC+4.

==================================================

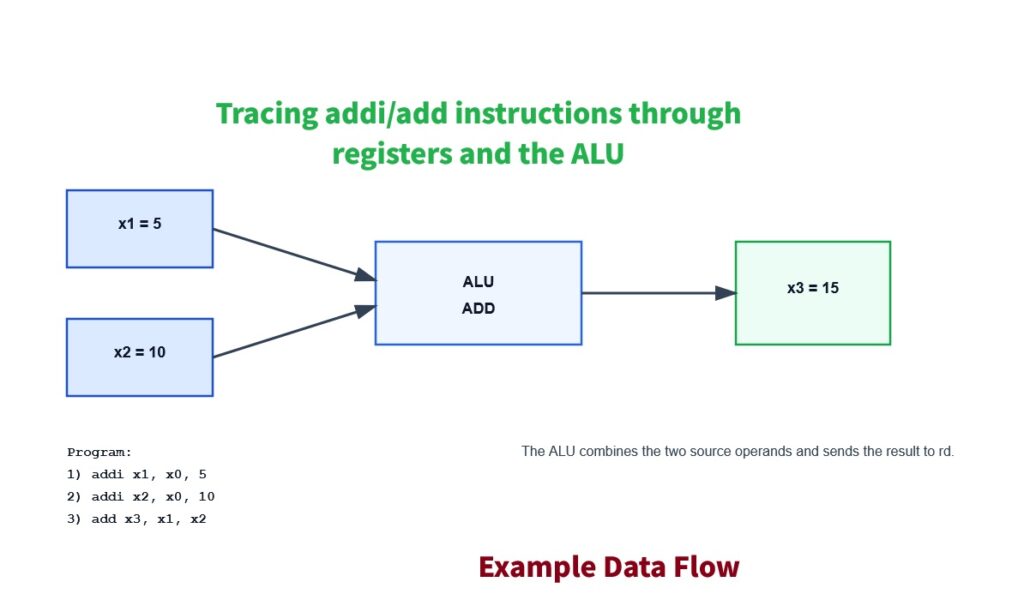

5. First RV32I Example

Code:

addi x1, x0, 5 addi x2, x0, 10 add x3, x1, x2

Meaning:

- x0 always contains 0

- addi x1, x0, 5 => x1 = 0 + 5 = 5

- addi x2, x0, 10 => x2 = 0 + 10 = 10

- add x3, x1, x2 => x3 = 5 + 10 = 15

Final register values:

x1 = 5

x2 = 10

x3 = 15

6. Step-by-Step Execution Trace

Initial state:

- PC = 0x0000

- x0 = 0

- all other registers assumed 0 for this example

Trace:

Step 1

PC = 0x0000

Instruction = addi x1, x0, 5

Operation = x1 = x0 + 5 = 0 + 5

Result = x1 = 5

Next PC = 0x0004

Step 2

PC = 0x0004

Instruction = addi x2, x0, 10

Operation = x2 = x0 + 10 = 0 + 10

Result = x2 = 10

Next PC = 0x0008

Step 3

PC = 0x0008

Instruction = add x3, x1, x2

Operation = x3 = 5 + 10

Result = x3 = 15

Next PC = 0x000C

7. Why Assembly Language Matters

Assembly helps you understand:

- how high-level languages become machine instructions

- how loops and functions really work

- how CPUs use registers and memory

- why pipeline hazards and performance issues happen

When you learn assembly, you understand what the hardware is actually doing.

==================================================

8. Preview of the Full Tutorial

This 10-file tutorial covers:

- Introduction to RISC-V and RV32I

- Registers and core machine model

- Instruction formats and encoding ideas

- Arithmetic and logical instructions

- Memory access and addressing

- Control flow, branches, and loops

- Functions, stack, and calling convention

- Arrays, strings, and complete small programs

- Pipeline, forwarding, stalls, and hazards

- Mini project, debugging, and advanced review

==================================================

9. Key Terms

ISA

Instruction Set Architecture, the interface between software and hardware

register

very small fast storage inside the CPU

memory

larger storage outside the register file

PC

Program Counter, address of current instruction

immediate

constant value encoded inside the instruction

==================================================

10. Exercises

- What does the “32” mean in RV32I?

- What does the “I” mean in RV32I?

- Why is RISC-V called an open ISA?

- If instructions are 4 bytes each, what is the next PC after address 0x0010 in normal execution?

- In the example program, what value ends up in x3?

- Why is x0 useful?

- Write your own 3-instruction program that places 12 into x5 using addi.

- Suppose PC starts at 0x1000. After three normal instructions, what is the PC?

==================================================

11. Exercise Answers

- It means 32-bit architecture.

- It means the base integer instruction set.

- Because its specification is open and free to use.

- 0x0014

- 15

- It provides a constant zero, useful for moves, comparisons, and initialization.

- One possible answer:

addi x5, x0, 7

addi x6, x0, 5

add x5, x5, x6 - 0x100C