1. Instruction Set Encoding

This article will continue the introduction of RISC-V and introduce the encoding structure of the RISC-V instruction set, as well as the characteristics and classification of the RISC-V instruction set.

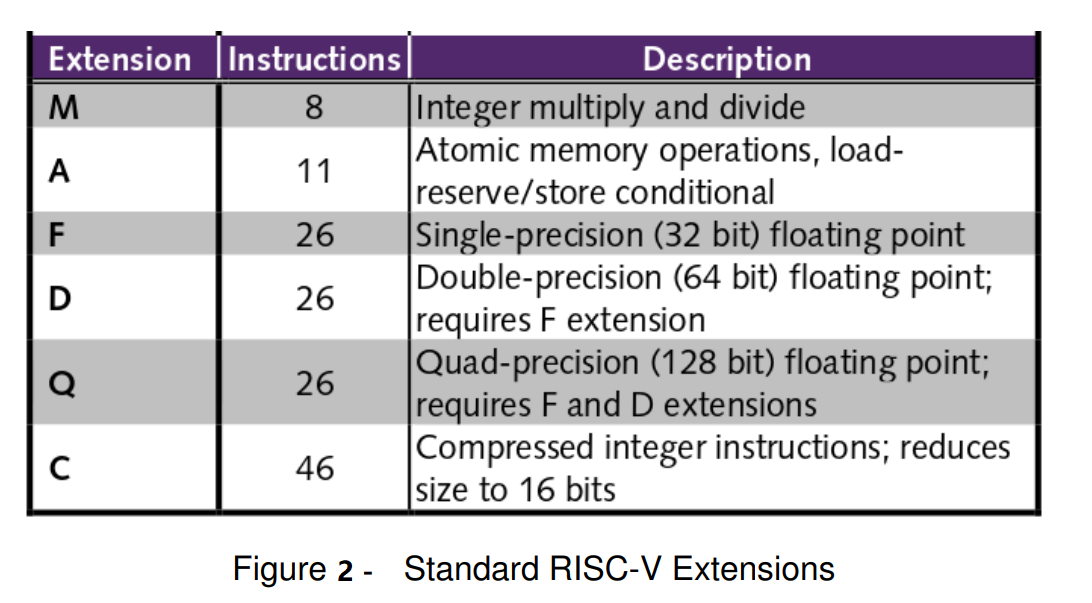

The instruction length can be divided into 16-bit, 32-bit, 48-bit, 64-bit, 128-bit, etc. according to the instruction encoding, as shown in Figure 1.

- 16-bit instruction length: The instruction is 16 bits long, with the lowest two bits being “aa”, which can be 00, 01, or 10 (aa cannot be 11). If aa is 11, then the instruction length is always 32 bits or more.

- 32-bit instruction length: The instruction is 32 bits long, with the lowest five bits being the indicator “bbbaa” of the instruction length. “aa” must be 11, and “bbb” must be 000-110 but cannot be 111.

- 48-bit instruction length: The instruction is 48 bits long, with the lowest 6 bits being 01_1111. In practice, no manufacturer or individual supports the development of a 48-bit CPU.

- 64-bit instruction length: The instruction is 64 bits long, with the lowest 7 bits being 011_1111.

- 80-192 bit instruction length: The lowest 7 bits are 111_1111, and the 12th-14th bits are “nnn”, which cannot be 111.

- 128-bit instruction length: The instruction is 128 bits long, with the lowest 7 bits being 111_1111, and the 12th-14th bits “nnn” being 011.

- Instruction length greater than 192 bits: The lowest 7 bits are 111_1111, and the 12th-14th bits “nnn” are 111.

2. Characteristics and Advantages of Instruction Set Encoding Structure

The main advantages of the encoding structure are as follows:

- It enables the rapid identification of the instruction length, whether it is 16-bit, 32-bit, 48-bit, 64-bit or 128-bit, providing a fast and concise recognition for the instruction decoder.

- It facilitates the designer to mix and match different instruction architectures with different bit lengths, making it easier for code optimization.

- The compressed instruction set module (C) contains 46 instructions of 16-bit length, but all 46 instructions are not independent, they are just compressed under special conditions in 32-bit instructions. Therefore, each 16-bit instruction can find the prototype of a 32-bit instruction, so it can be translated into a 32-bit instruction by hardware or software before instruction decoding. Instruction decoding and execution can still be performed in the same way as 32-bit instructions. Therefore, if translated into 32-bit instructions before decoding, the compression format is invisible during subsequent execution.

3. Instruction Set Modules

3.1 Standard Configuration Modules

“RV32I, RV32E, RV64I, RV128I” are different variants of the RISC-V instruction set architecture.

- RV32I and RV32E are similar and share most of their instructions, with RV32E being a subset of RV32I. RV32I defines 32 general-purpose registers, while RV32E only uses 16 of them.

- RV64I is an extension of the RV32I, with 64-bit registers and 64-bit addressing.

- RV128I is a further extension that supports 128-bit addressing, and is intended for use in systems with a large address space, such as those used in scientific computing and data centers.

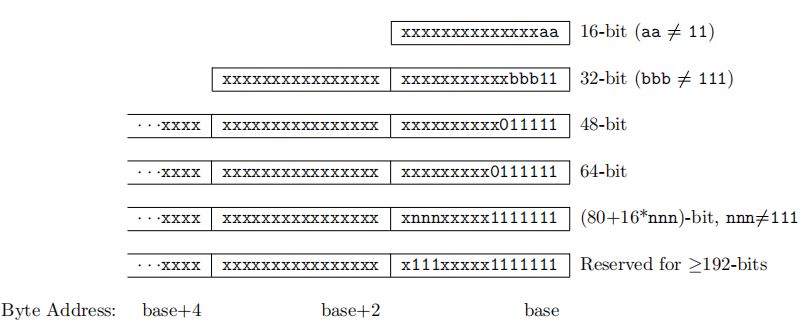

3.2 Expanded Instruction Set, as Shown in Figure 2.

- M: Integer multiplication and division instructions

- A: Memory atomic operations and Load-Reserved/Store-Conditional instructions

- F: Single-precision (32-bit) floating-point instruction set

- D: Double-precision (64-bit) floating-point instruction set

- Q: 128-bit floating-point instruction set requires F and D extensions

- C: Compressed instruction set, with instruction length of 16 bits