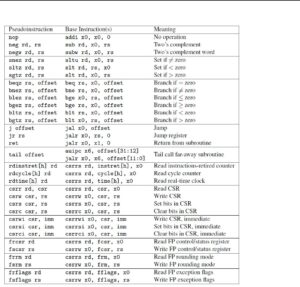

RISC-V Pseudo-Instruction Lookup Table Assembler Pseudo-instructions The assembler implements a number of convenience psuedo-instructions that are formed from instructions in the base ISA, but have…

The two U-type instructions introduced here operate on the program counter (PC) rather than the general-purpose registers (x0-x31), and are represented by the AUIPC opcode.…

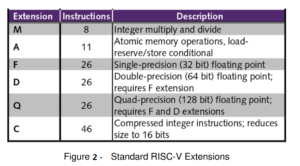

1.RISC-V Introduction the Origin of RISC-V, and the Features of RISC-V RISC-V Instruction Set Architecture Features and Classification RISC-V Instruction Set Encoding Structure, Features and…

1. Instruction Set Encoding This article will continue the introduction of RISC-V and introduce the encoding structure of the RISC-V instruction set, as well as…

RISC-V is an open-source instruction set architecture (ISA) that was originally developed at the University of California, Berkeley in 2010. The project was led by…