This article will start with the I-Type integer register instructions and provide a detailed introduction to each assembly instruction and its specific implementation. 1. I-type…

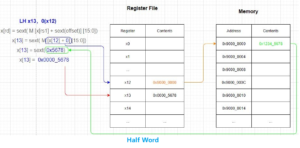

1. Load Store Instructions RV32I is a load-store architecture. Only load and store instructions can access memory and peripherals (registers inside the CPU can only…

1.Control Transfer Instruction In RV32I, control transfer instructions are mainly divided into two categories: unconditional jump and conditional jump. 2. Unconditional Jump Instructions Unconditional…

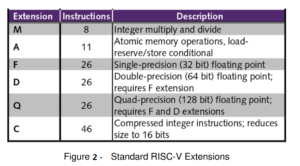

1.RISC-V Introduction the Origin of RISC-V, and the Features of RISC-V RISC-V Instruction Set Architecture Features and Classification RISC-V Instruction Set Encoding Structure, Features and…

1. Instruction Set Encoding This article will continue the introduction of RISC-V and introduce the encoding structure of the RISC-V instruction set, as well as…

RISC-V is an open-source instruction set architecture (ISA) that was originally developed at the University of California, Berkeley in 2010. The project was led by…